您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2021-12-29 16:36

1. 引言

独学而无友,则孤陋而寡闻;

2. 背景介绍

某控制器产品在做认证测试中,ESD ±6KV接触放电出现通讯故障死机问题,需要重启后可恢复,针对此问题进行分析和整改。

3. 分析与整改

3.1 控制器组网与实验点

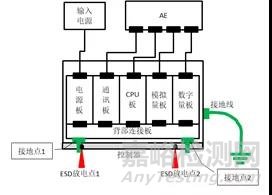

控制器组网与ESD放电点示意图参见图1所示。

(a)组网与放电点示意图

(b)放电点实物图

图1 控制器组网及实验点

3.2 试验现象

ESD接触放电±6KV,对放电点1和放电点2进行试验时(每个点放电3-6次左右),及放电点3(每个点放电10-20次左右)就会出现通讯故障,无法与上位机通讯,处于死机状态,需要重动恢复。放电点4试验无问题。

3.3 接地可靠性排查

3.3.1 接地点阻抗测定

利用万用表对盖板接地点阻抗测定,结果如下:

表1 接地阻抗

|

盖板接地点 |

接地阻抗 |

备注 |

|

接地点1 |

0.2-0.3Ω |

接地阻抗较大,接地效果不好 |

|

接地点2 |

0.2-0.3Ω |

|

|

接地点3 |

0.1-0.2Ω |

接地阻抗大,接地效果不佳 |

|

接地点4 |

0-0.1Ω |

一般可接受 |

注:ESD频谱达到GHz频段,利用万用表进行机壳接地阻抗值是不准确的,但可以做为初步的定性分析判断。

3.3.2 机壳接地点变更排查

对控制器的接地点位置进行人为变更,对各放电点进行ESD实验,验证各接地的可靠性,详细结果参见表2。

表2 机壳接地点变更实验结果

|

盖板放电点 |

实验结果 |

|

|

初始实验接地配置 |

放电点1 |

Fail |

|

放电点2 |

Fail |

|

|

放电点3 |

Fail |

|

|

放电点4 |

Pass |

|

|

接地点变更:靠近接地点2 |

放电点1 |

Fail |

|

放电点2 |

Pass |

|

|

放电点3 |

Pass |

|

|

放电点4 |

Pass |

|

|

接地点变更:靠近接地点1 |

放电点1 |

Pass |

|

放电点2 |

Fail |

|

|

放电点3 |

Fail |

|

|

放电点4 |

Pass |

|

3.3.3 接地可靠性排查小结

(1) 接地点位置变更后到2后,放电点2/3/4实验没有问题,但放电点1仍然会导致通讯故障死机;接地点位置变更后到1后,放电点1/4实验没有问题,但放电点2/3仍然会导致通讯故障死机。

(2) 盖板与机壳地搭接不良,接地点1/2/3接地阻抗较大,接地点4的阻抗可接受;

(3) 整体的控制器盖板与机壳的搭接设计不可靠,导致ESD测试中会出现问题。

3.4 接地不良导致通讯故障死机问题分析

3.4.1 ESD耦合机理分析

3.4.1.1 ESD波形参数

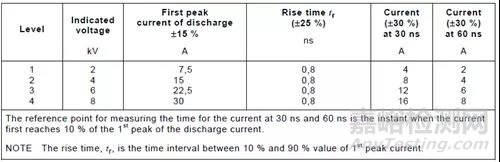

IEC61000-4-2标准中ESD放电电流波形参数如图2所示[1],6KV的放电电流峰值为22.5(1±15%)A。

图2接触放电电流波形参数

3.4.1.2 ESD频谱特性

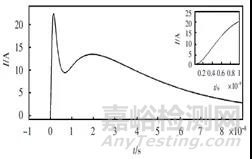

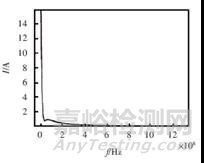

6KV等级ESD的放电电流与频谱特性参见图3和图4所示[2]。ESD的幅值一般在频率0~1.2 GHz 间,超过1.2 GHz 幅值基本衰减为0,整个频率期间出现了2 次峰值.频率在0~30 MHz 间,幅值逐渐衰减,并且衰减较快.然后随频率增加至60 MHz 时,幅值达到第二个峰值,随着频率继续增加,幅值逐渐衰减至0。

图3 6KV放电电流波形

图4 6KV接触放电电流频谱

3.4.1.3 ESD放电耦合机理分析

(1) ESD的干扰模式

ESD以共模干扰方式对控制器进行干扰,主要有以下几种形式:

◆ ESD放电中形成的场耦合,一般发生在接地点良好,但接地位置附近有敏感信号或走线的情况:

◆ ESD放电电流在接地阻抗路径中形成噪声电压Vnoise干扰敏感设备,一般发生在接地不良,接地阻抗较大的情况;

◆ ESD放电电流直接注入敏感信号中,一般发生在对pin进行ESD注入实验的情况。

(2)结构地分析:

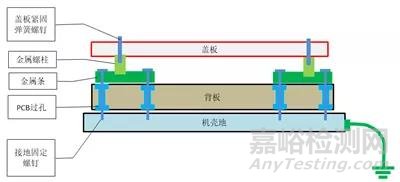

控制器盖板接地的结构层次:盖板紧固弹簧螺钉→金属螺柱→金属条→接地固定螺钉→机壳地。PCB过孔无接地铜盘,与金属条和机壳均无搭接。金属条与机壳的搭接仅仅通过螺纹进行,搭接不可靠,阻抗大,结构接地详见图5所示。

(a)盖板接地点实物图

(b)盖板接地结构示意图

图5 盖板接地结构

(3)干扰路径与等效机理电路分析

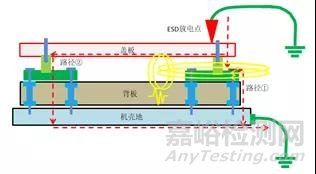

◆ 当盖板与机壳地间的接地良好时,阻抗足够低,与机壳形成等电位搭接,无压差。

ESD的主要放电路径为图6中的①和②,因①的接地物理路径较近,大部分干扰会从①路径中流到大地。流过路径①附近的电流形成的干扰场,会串扰周围的敏感信号或敏感走线。

图6 ESD放电路径示意图

◆ 当盖板与机壳地间的接地搭接较差时(搭接阻抗较大),ESD放电电流会在搭接点处形成噪声电压Vnoise。

噪声电压通过盖板与PCB板件的分布电容,形成干扰电流流过PCB,使得敏感干信号受干扰,参见图7所示。

图7 接地不良的ESD耦合机理示意图

(4)干扰噪声估算

通过接地阻抗测定与接地点变更ESD实验结果,结合ESD的干扰机理,可以确定控制器为ESD放电电流在接地阻抗路径中形成噪声电压Vnoise ,干扰了内部敏感信号。

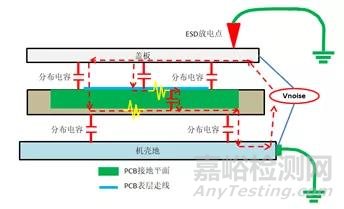

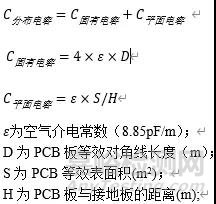

◆ PCB与结构件间的分布电容估算

PCB板与盖板间的分布电容可用以下公式进行估算[3]:

控制器的PCB尺寸为15cm*40cm,与盖板距离3cm,与机壳距离2cm左右。PCB接地参考地层与盖板间的分布电容约为33pf。

◆ 盖板与机壳间搭接处的噪声电压估算

6KV接触放电的放电电流峰值实测约为24A左右,接触阻抗为0.3欧姆,电压约为7.2V。

注:盖板与机壳间的搭接阻抗为万用表测试结果,实际的ESD频段的搭接阻抗值要大于0.3Ω,本文暂以0.3Ω为例进行计算说明。

◆ 流过背板的电流:

I1=C*2πf*U=33pF*2*3.14*1.2GHz*7.2=0.25A。

注:为方便计算,ESD频段扩展到1.2GHz。

◆ 流经背板PCB参考地平面的噪声电压:

Vnoise=I1*Z=0.25A*3mΩ=0.75mV;

注:PCB的铺地平面阻抗一般为mΩ级别,结合背板的过孔数量,估算PCB铺地平面阻抗为3mΩ。

◆ 流经背板PCB表层走线的噪声电压:

I2= C*2πf*U=3pF*2*3.14*1.2GHz*7.2=0.025A(流过通讯指示灯走线的电流)

Vnoise=L*di/dt=300nH*0.025A/(0.8ns)=9.4V。

注:背板表层通讯指示灯为最长走线,长度为20cm左右,走线宽度为10mil,电感量为300nH左右。指示灯走线与盖板间的分布电容约为3pf。

3.4.2 通讯故障死机问题原因排查

(1)通讯故障死机原因有二:通讯板受干扰或者CPU板受干扰。

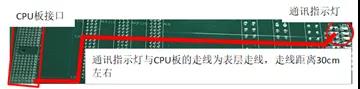

进过排查,定位到是因为通讯指示灯走线过长(隔断走线后无问题),导致ESD干扰耦合到背板通讯指示灯走线,噪声电平达到9.4V的高频干扰进入CPU板。9.4V的噪声电压足以干扰CPU板的敏感信号(1.2V、3.3V、5V等级的敏感信号),可以通过滤波电容、磁珠、TVS管等方法进行抑制。

图8 通讯指示表层灯走线示意图

(2)CPU导致死机原因有二:3.3V电源受干扰或时钟受干扰。

通过前述分析,地平面上的噪声电压为0.75mV,不足以干扰3.3V电源。经过排查确认ENC28J60的时钟受干扰,导致出现通讯故障而死机。

3.5 整改与验证

因客户要求不能整改PCB内部电路及外观可见措施,只能从结构接地下手。

◆结构地搭接整改:

针对盖板与机壳间的四个接地点通过铜箔加强接地,整改措施如下。

|

整改前 |

整改后 |

|

|

|

◆实验验证:实验采用±7KV等级无问题。

3.6 落地设计

最终落地设计为背板的表面和底面四周进行铺铜处理,加强盖板与结构地的搭接。实验验证无问题,落地措施参见下图。

图9 背板与机壳间的搭接处理

4. 思考与启示

(1)ESD干扰以共模形式串入PCB线路或通过空间场耦合干扰敏感信号,需要解耦分析;

(2)对于接地点可靠性的排查,可通过人为改变接地位置进行故障问题的分析;

(3)ESD抑制的一大手法是接地,要确保放电点与机壳地搭接的可靠性,保证搭接阻抗在ESD频段范围内足够小,不足以形成干扰电压;

(4)PCB敏感信号或与敏感信号相关的信号线,避免在表层长距离走线而引起的干扰,无法避免时,注意信号换板连接器附近的滤波处理。

(5)ESD敏感信号在设计前期需要进行ESD干扰评估,特别是噪声等级的评估,有利于抑制器件的选型,同时在PCB板进行干扰风险规避是成本最低,效果最好的方法。

(6)ESD的抑制手段多样化,除了接地对ESD干扰进行泄放外,还可通过滤波、屏蔽、瞬态抑制、隔离、放电敏感距离控制、采用绝缘类材料阻断放电等等手段进行抑制,结合设计需求落地。

5. 参考资料

[1]. IEC61000-4-2. 2008.Electromagnetic compatibility (EMC) –Part 4-2: Testing and measurement techniques– Electrostatic discharge immunity test [S].

[2].阳长琼.不同电压等级静电放电频谱分析[J].兰州交通大学学报. 2018(5):18-22+28.

[3].郑军奇. EMC设计分析方法与风险评估技术[M].北京:电子工业出版社,2020: 84-85.

来源:电磁兼容EMC