您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2024-07-01 08:28

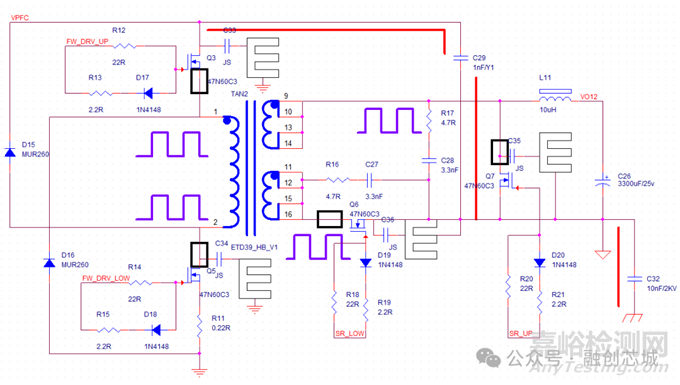

G0752是一个有连续模式的PFC,双管正激、同步整流、反激待机等技术的电源。这个电源在进行Class B的测试传导时遇到一些问题,也想了解决办法,虽说有些理论没有很容易的讲清。虽说有些动作没有办法讲明动机,但我也是尽量的将其写出来,还原整个调试过程。

为了简单有效果的排除传导干扰源,所以我是先关闭了正激部分的电路,只让辅助电源的反激和PFC在工作。目的是先解决PFC和反激的问题,然后解决正激的问题,这样能更加清楚的定位故障点。比如:我发现在正激关闭时20MHZ处的超标,其他地方没有明显超标。而当我把正激开起来后,发生13MHz也有明显的不良,所以可以简单的定位故障点。

反激和PFC部分

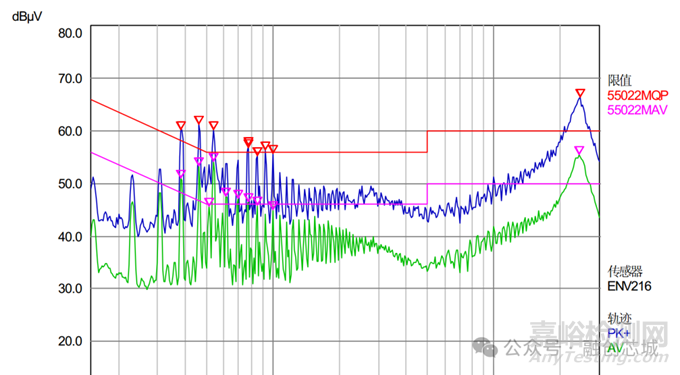

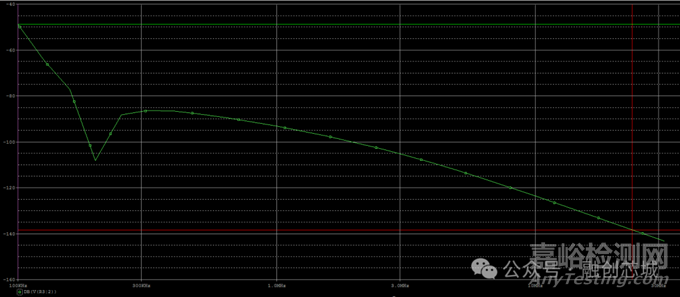

这是反激带20W,正激关闭时的传导扫描的波形,可以发现在500K~1MHZ有十分强烈的干扰。而且传导测试在低频段的波形与PFC的开关频率相同,此时PFC开关频率约为80KHZ。只有后面在25MHZ附近有超标,虽然很严重。所以针对这个问题,主要是要先解决低频段反激和PFC超标的问题。

▲ 正激断开,反激带20W

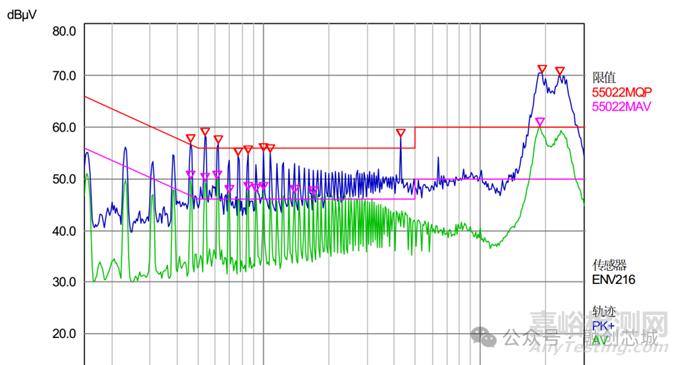

作为对比,测试了正激带半载时的传导的波形,可以看到的是正激的加入后引起了18~20MHZ处的超标,见下图(很明显的看出因为正激加入引起波形的不同,在150K处因为带了负载,所以流过L/N的差模电流加大。所以150K处的问题主要是肯定是X电容和差模电感的组合问题,可以通过不同的X电容和共模电阻的配合来解决这里的超标的问题)。

于是我使用了LL18和LL29(内部代号,18磁环外接20,电感量越15mH LL29外接18,电感量18mH),企图使用更大的电感量来抑制低频500K~1MHZ处的超标,可是结果不是很明显的。因为使用了不同的电感,是的原边在20MHZ的超标,超的更多的了。

于是我的调整思路主要是被上图这个80KHZ频率的PFC波形所引导了,我企图通过降低PFC的开关速度(加大驱动电阻)、使用SIC二极管、在MOSFET和二极管上磁珠、在MOSFET上加一定的吸收、为PFC的散热片的接地覆铜,各种手段,对付500K~1MHZ处的超标依然是没有很好的解决,于是我冷静下来想了一下PFC部分传导干扰的模型。

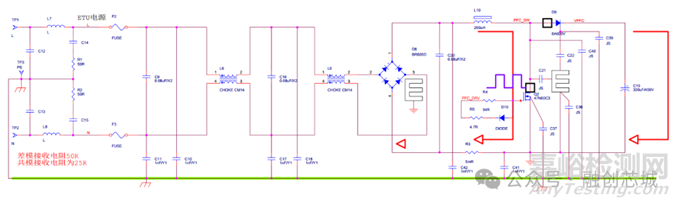

下图是一个简易的PFC传导测试模型,LISN测试两个50R的电阻的电压来判断传导干扰是否超标。减小LISN上被检测的电压最间的办法就是,减少流过这个50R电阻的电流。电源内部的差模电流主要是靠X电容和差模电感来抑制,也可以通过减少电流环路面积,加大大电解电容来缓解差模电流的问题。重点是难搞的共模干扰电流如何来减少?标准的传导测试是在一个木桌上,距离地面有一个大的接PE(接地阻抗极低)的铁板,被测电源和负载(通常用电阻)放在桌子上进行测试。

在电源内部的干扰电压(一般在开关拓扑的开关节点,在图中我使用了紫色方波标志)会通过干扰点和接地(PE)的铁板之间的寄生电容通过高频电压激励位移电流来形成共模干扰电流,干扰电源是电压源(类似电压源)。位移电流通过寄生电容流到接地的铁板,干扰电流必须要回到干扰源(电流是要走一圈的)。如果干扰电流到了铁板,然后通过电源端子上的Y电容回到了L/N线上,在通过二极管桥返回干扰点(高频电压节点)。则是极好的,干扰电流虽然在PE上走了一圈,但是没有从LISN内部走,两个50R的电阻上的电压是没有收到这个干扰电流的影响的。因此加在端口上的Y电容立功了,这个Y电容提供了干扰电流返回的路径(当然在这里干扰电流是不一定要走端口的Y电容的,电流是会走最低阻抗的路径。对高频干扰电流而言,PCB上走线过长、过窄、寄生电感过大,都会使干扰电流回流的阻抗变大,从而使电流要走LISN上走,于是被接收机测到了)。

我在上图上标注了几个明显的干扰点,在PFC上MOSFET和DIODE的开关节点是电压变化率是很高的(电压值也很高0-400V的在变),特别是二极管的反向恢复也会加剧这里的电压变。而且MOSFET和DIODE都安装在一个散热片上,管子内部到散热片的寄生电容会对散热片注入很大的位移电流。散热片如果没有非此低的阻抗接地(也就是散热片的接地点必须是要靠近MOSFET或DIODE的,MOSFET>HS的寄生电容流过的电流要通过散热片的接地点返回到MOSFET中,这样才能减弱干扰电流对外发射。),我在图中建议的标志了几个电容:1、MOSFET到散热片,2、DIODE到散热片,3、PFC_SW到PE,4、散热片到PE,5、PFC电感到PE。

我们思考有这种一种情况,PFC_SW节点对PE铁板的寄生电容流过干扰电流,干扰电流在铁板上走一圈,要回到PFC_SW这里。所以要从LISEN或端口进入电源,走LISN就会被接收机测试到。只有从铁板到端口PE这条线,然后通过Y电容返回L/N回到PFC_SW这里。但是我们假设有这么一种情况,从端口到电源上Y电容的左线上寄生电感较大,对高频有较大的阻抗,电流没有低阻抗的路径。就只有从LISN走了,即使你在L/N,直流母线都在Y电容到地。其实没有意义,毕竟干扰电流是从接PE的铁板返回到端口的,这里的阻抗大,Y电容也毫无意义。

加入从PE到电源端子,电源端子到电源内部的PE走线的阻抗非常小,从干扰接地通过寄生电容到PE的电流,都可以通过端子进入电源。干扰电流顺利的从PFC_SW到寄生电容到铁板到端子到PE走线到L/N的Y电容,到桥后整流母线的Y电容返回源头。(也就是说只有电源上PE的走线阻抗非常低,放在桥后直流母线上的Y电容才有意义。)现在是将干扰电流的流动路径,下面是减少干扰电流的强度。建议的办法就是,减少PFC_sW这里开关节点的PCB布局面积,通过合理的吸收减弱这里的dv/dt,减慢PFC开关的速度,通过加磁珠消耗干扰点的干扰能量,散热片的就近接地。这些都是减弱干扰点对外发射的办法,但是我们通常忽略PFC电感。这个电感上有0~400V的电压变化,而且通常体积还不小,所以有办法的话最好对电感进行包铜带,减弱对外的发射。通过这些办法,终于对PFC在500KHZ~1MHZ处的干扰有了抑制,见下图:

在后面的整改中又对应着将板上滤波器的元件的数量减少,之前是有3对Y电容3个共模电感3个X电容。首先取消的是一个LL023的共模电感,这个电感的磁芯是使用T25*15*10绕了30圈,电感量约在5mH。由于绕线匝数较多匝间电容较大,这个电感对付高频信号,没有明显的厉害之处。首先去掉这个电感后,差模150K~1M之间的值有所增加,然后13M附近也有一定的升高。特别是在23M附近会上升的更加明显,基本上是要压着线了。我又开始取消Y电容,首先是把两个共模电感之间的Y电容去掉,发现在23M的尖峰升到了非常高。我当时是非常害怕的,怕好不容易搞好的传导又被搞砸了。于是我又把整流桥前的Y电容加上去,结果是一样的。23M附近的高频超的很高了。

回忆自己的动作发现只是去掉了三组Y电容中的两组,然后只是保留了端口第一级和整流桥前面的一级,在两个共模电感之间的Y电容被我去掉了。于是我把在两个共模电感之间的Y电容加了上去,再次测试结果在23M附近的超标点(约到75dB),下降了Class B的传导限值之内,还有一点点的余量。于是我再次去掉了端口第一级的Y电容,发现这个Y电容对该板的传导测试结果影响不是很大,于是就取消了。到目前为止,已经取消了1个共模电感、一对Y电容。

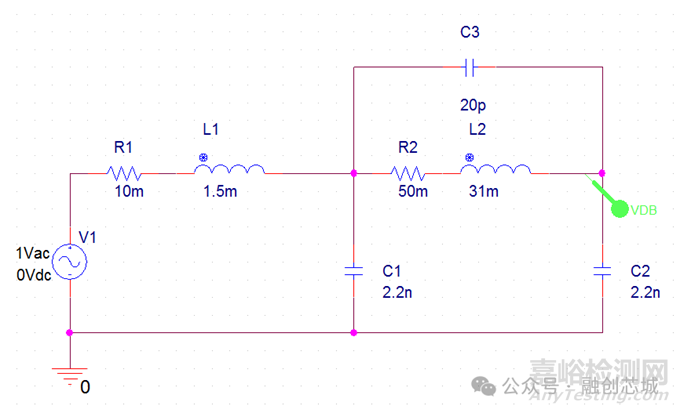

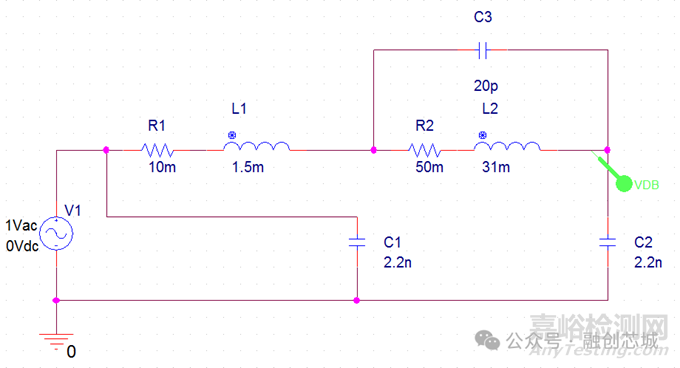

在后面我通过仿真分析,在共模电感中间的Y电容对滤波器的性能的影响,见下图。现在在该板上使用的共模电感组合是一个绕了40~50圈的共模电感电感量在30mH,另外一个是双线并绕只绕了15圈的电感,其匝间电容相对来说要小一些。为了简易的分析滤波器的性能,对大电感量的寄生电容假定为20p,另外一个电感假设没有电容。现在是仿真Y电容放在两个共模电感中间的效果:

进行频率响应,起点在100KHZ,结束点到30MHZ,10倍频扫描,见结果在23M附近有138dB的衰减(实际肯定没有这么高,我们仿真只是验证一下理论)。

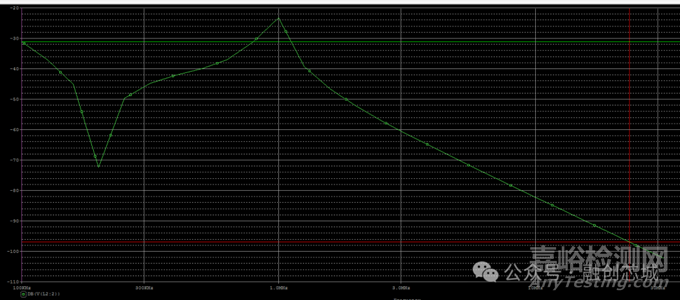

我现在改变Y电容的外置,把放在两个共模电感中间的Y电容放在第一个共模电感前面,结果是:

结果Bode图的差异很大,在23M附近找个接法只有衰减96dB,差别相当的大!

因此这个Y电容的位置可谓是相当的关键,也因此我去掉这个Y电容后,在23M附近居然会超标了15个dB,当我找到这个突破点后,我把这里的Y电容用成了2.2nF的。电容加大一倍,对滤波器的衰减更加有效果,在更改Y电容和确定删减位置后,再次扫描的传导,发现在10M~30MHZ处之前的超标的点,现在已经得到控制。这个案例也说明在高频段,然任何一个Y电容对结果的影响都是十分的关键。

好了,Y电容和共模电感的的删减已经可以确认,而且对传导的结果影响不是很大。因为板上使用了三个X电容,板上位置有限,不能使用三个电容,必须是要取消一个。分析传导的波形,发现在150K后面一点点有个十分明显的尖峰。在加大X电容效果都不是很明显,只有串联一个差模电感才能很好的抑制这个点。如何处理呢?臧工指出在低频150K~1MHZ的低频内,超标的能通过合适的共模电感和X电容来强行压下来,也可以改善电路的工作来达到改变。观察波形在低频500K~1MHZ的超标的尖峰频率间隔可以看到一个PFC的开关频率约为80K,我尝试减慢PFC开关管的开关速度,在PFCMOS上并联吸收都不能很好的解决。后面是通过对PFC电感外侧包铜带并连接到大电容的负,减弱了部分低频段的超标。但是在150K后面这个超标,始终都没有得到解决。因此我们想到的办法是降低开关频率,因为目前PFC的开关频率约为80K,所以在开关频率的2倍频,160K处有个非常高的尖峰,正好被接收机收到。如果把开关频率降低到70K,那么2倍是在140K,也是恰好避开了这个150K的点。减小开关频率并加大电感量后,再次上电。传导在150K处的波形得到抑制,只是在200K附近有一个尖,但是这里的幅值是比较小了,在传导的限值之内,所以可以说在低频段是很好的控制住了。于是我们删掉了在两个共模电感中间的X电容,扫描发现低频150~1M已经压线了,并且没什么余量。而且中频1~10M也开始有些余量不够,因此需要想办法来提高这个区域的余量。

关于地线,将三线接入变为两线接入后虽然将PE铁板到电路中的连线断开,但是板上PE还是和副边通过电容进行了高频连接。在实际扫描后发现在两线接入后仅在低频500K~1MHZ处有明显的变大,在1M~10M则是也是有上升,有些接近超标,但是在10M~20M却变得很好,之前有明显尖峰的点,都有一定的下降。高频段的波形总体是要比三线接入的要好。将三线接入变两线,传导波形有一定的好处可能是:原边到副边的干扰,走一圈之后只能通过副边到PE的电容,然后PE到Y电容返回,干扰信号被闭合在了电源里面,由于没有PE,所以有些干扰电流不会流入到LISN,也不会被检测到,所以传导的波形好了一点点。我在板上做副边到PE的连接是通过一个多股并绕的铜线,距离大约20cm。高频来看这根导线的阻抗可能会比较大,导致副边的到PE的这条路径上的阻抗较大,干扰信号更愿意从LISN走,通过Y电容到原边,这样来走一圈。臧工觉得使用20cm长度的铜线接PE对20MHZ的高频来看,阻抗是很大的,这样肯定是对传导的高频有一定的阻碍。但是我们的电路板实际是行安装在金属外壳上的,金属外壳作为优异的导线,其面积较大,对高频信号的阻抗而言绝对比20cm长度的铜线要很好多。

当我们安装一个模拟机壳的U型壳后,再次进行传导测试。发现在500k~10MHZ的波形都比之前有了较大的减弱,很明显低阻抗的接PE对传导的测试非常重要。由于使用了铁板做接地,传导150K~1M处的超标得到很好的控制。这样也就把3个0.68uF的X电容去掉了一个,板上只使用了两个。但是在传导高频段10M~30M的,却有了13M和23M两个地方接近超标,有几个尖峰冒的高,最高处(23M)有2dB的超标。但是谐振在板上就使用了2个X电容,4个Y电容,2个共模电感。比之前使用3个X电容,3个共模电感,6个Y电容,滤波器的体积和成本已经得到了控制。

滤波器的组合问题,由于低频段需要差模电感配合X电容强化衰减的问题得到解决。目前需要调整共模电感的原因就是,调整共模电感量来达到对13M和23M这两处冒出的尖峰进行处理。使用T25*15*10磁环绕50圈达到30MH的大共模对低频150K~10M的强大滤波不用质疑,但是这个电感匝间电容大,对高频信号的抑制基本没有了作用。对付10M~30M的共模干扰主要就靠这个小电感,我的希望是它的寄生电容足够高,磁性材料的高频性能足够好,对兆级别的信号依然能有一定的抑制作用,不会因为寄生电容和磁芯材料的频率响应才为滤波器的短板,可是实际就是这样的。我使用了同时桌子上现成的一款,L/N双线并绕磁芯体积外径约为20mm,绕了大约10圈,电感量在1.4mH。替换之前只有6圈 800uH的电感,在上电测试传导后,发现13M和23M两处的尖峰明显得到抑制,至少是下降了2.5个dB,在如此明显的效果上,实在是令人兴奋。于是我动手绕了一个T25*15*10的磁环,双线并绕,在保持一定的匝间距离的情况下,约绕了15圈,电感量在3mH,替换1.5mH的电感后,高频段的余量继续加大,因此该板的传导问题可以得到了解决。

反激部分

在反激中有三个典型的电压动点(变压变化率相当高):就是MOSFET的VDS,这里包含RCD二极管的反向恢复时的干扰、副边整流二极管、辅助绕组上的整流二极管。针对共模干扰主要是高dv/dt通过对铁板的寄生电容,通过位移电流的方式产生干扰。干扰电流要通过接PE的Y电容返回整流桥,在通过L/N返回干扰源。减少反激传导干扰最简单的控制办法就是,减弱这几个电压动点的变化率。比如加强RCD的吸收,在MOS的漏极加磁珠、在副边整流二极管加磁珠、然后把辅助绕组的整流二极管使用较为慢速的管如RS1M。对于反激RCD的二极管,最好是使用慢管如1N4007。这样就可以比较强的减弱反激辅助电源的干扰。然后处理好副边接地到PE的电容这条路径,可以较为强化的抑制共模干扰。最后的一招就是减弱了反激开关MOS的开关速度,正向100R,反向22R。臧工是认为管子的耗损,开通是一部分,但是关断部分的损耗是要大于开通时候的。这也是因为在关断时,流过管子的电流处于峰值状态,因此如果关断速度较快的话,是可以稍微减少开关耗损的。也因此,对于控制MOS的开关来说,只要关断的电阻低于22R,管子的耗损是可以接受的。

最后为了控制反激部分MOS管子的电磁干扰,我们在后续的板子上要加上一个小的散热铁片,并且铁片是要就近连接到GND上。一方面是提供了管子的散热, 另一方面也对管子对外电磁发射有了闭合的路径。

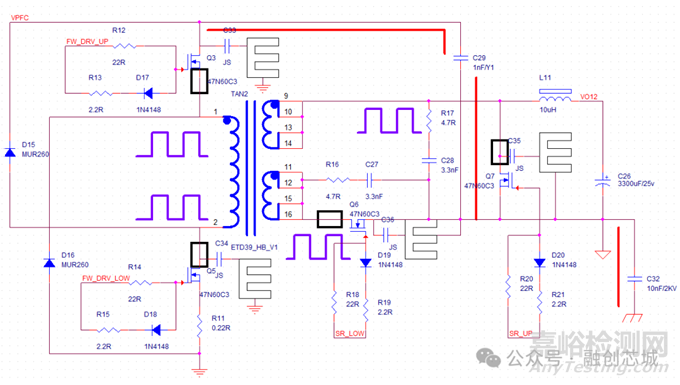

正激部分

正激部分原边的MOSFET上,虽然没有像反激那样因为漏感在VDS上有强烈的尖峰存在。但是因为正激变压器也会受到漏感的问题,虽然在VDS的电压上表现不出来(但是在电流上是可以看到因为漏感引起的尖峰,具体是表现在复位二极管上的电流,可以看到明显的反向恢复尖峰)。虽然正激的变压器没有那么强烈的电压变化,但是在变压器内部也是加了屏蔽层。屏蔽层的好处是减弱变压器内部的寄生电容,减少了原边绕组流到副边的干扰电流。

由于正激在原边可以调整的部分是十分的少的,所以重点就只有放到了副边上面来。副边的干扰主要是来至同步整流的管子上的电压变化率,特别是续流管上,由于SRMOS的沟道和体二极管上的反向恢复干扰,引起的巨大的电压尖峰。这个点具体是表现在10M附近的干扰,考虑降低这里的干扰的出发点就是降低SRMOS的漏极上的电压变化率。最简单的处理办法就是减慢SRMOS的开关速度,由于这个管子的CISS电容较大,所以栅极的电压上升速度是比较慢的。这样可以使SRMOS的电流是先从体二极管走,由于栅极的电压上升速度较慢。所以有较大的电流从体二极管走后,栅极电压慢慢上升也意味着管子的沟道慢慢打开,所以减慢管子的速度后,在电路上的表现上是管子的VDS尖峰居然变得很低了。平台只有30V,尖峰只有43V。这样在传导上反应出来就是13M附近的点下降了很多,而且最新做出的修改就是把PCB的底层的一段覆铜取消,这样的目的是减少电压动点到PE铁板的寄生电容,减弱耦合到铁板上的干扰电流。

正激部分的干扰就是调整好SRMOS的漏极电压尖峰,减少覆铜的面积,稍微减慢开关速度。

来源:Internet