您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2024-10-11 18:26

《半导体器件的失效机理和模型》将针对硅基半导体器件常见的失效机理展开研究。这些失效机理大致按照从硅到封装器件的半导体生产工艺流程进行了分类:前段制程(FEoL)、后段制程(BEoL)和封装/界面失效机理。

各阶段常见的典型失效机理

前段制程(FEoL)常见的失效机理

1)与时间相关的电介质击穿(TDDB)-- 栅极氧化物

2)热载流子注入(HCI)

3)负偏压温度不稳定性(NBTI)

4)表面反转(移动离子)

5)浮栅非易失性存储器数据保持

6)局部电荷捕获非易失性存储器数据保持

7)相变(PCM)非易失性存储器数据保持

后段制程(BEoL)常见的失效机理

1)与时间相关的电介质击穿(TDDB)-- 层间电介质/低k值/移动铜离子

2)铝电迁移(Al EM)

3)铜电迁移(Cu EM)

4)铝和铜腐蚀

5)铝应力迁移(Al SM)

6)铜应力迁移(Cu SM)

封装/界面常见的失效机理

1)因温度循环和热冲击导致的疲劳失效

2)因温度循环和热冲击导致的界面失效

3)因高温导致的金属间化合物和氧化失效

4)锡须

5)离子迁移动力学(PCB)--组件清洁度

本文对FEoL阶段的负偏压温度不稳定性(NBTI)失效模式进行研究

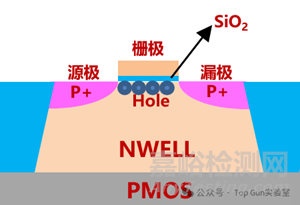

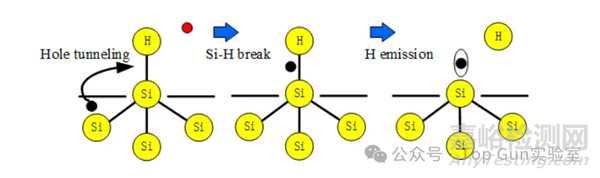

负偏置温度不稳定性(NBTI)是PMOS在沟道处于反型时所经历的一种磨损机制——当栅极负偏时,引起阈值电压逐渐漂移,高温下会加速该过程。NBTI是一种电化学反应,PMOS反型沟道中的空穴与Si/SiO2界面处的硅化合物(Si-H、Si-O 等)相互作用,Si-H被打断,留下带正电的界面态Si+(即施主型界面态),H被释放到栅氧化层中,在氧化层形成氧化层陷阱。

PMOS只要在反型状态下工作就会受到NBTI损伤。因此,NBTI对待机条件敏感(例如反相器的“0”输入)。即上图栅极施加负压,沟道进入反型状态;源极和漏极电压为零。

NBTI失效机理通俗的解释:当PMOS的栅极处于负偏压下,PMOS的Si/SiO2界面处会形成大量的Si-H键,在垂直电场作用下,产生的空穴和Si-H进行反应,使氢原子脱离,形成H、H-或者H2。

NBTI损伤是由反型沟道中的冷空穴损伤产生的,要注意不要将这种机制与在高VG状态下由碰撞电离产生的PMOS损伤(热空穴损伤)混淆。NBTI损伤可能导致PMOSFET的参数发生显著变化,特别是阈值电压绝对值的增加以及迁移率下降导致驱动电流减小。NBTI的电化学反应速度与栅氧化层电场(VG/tox)和温度强相关。

NBTI是限制CMOS亚微米技术缩放的一个因素,主要有以下两个原因:

1)NBTI与栅氧化层工艺强相关,氮氧化合物对NBTI比热氧化物更敏感。而为了在减薄栅氧化层时减少硼渗透问题(Boron penetration),必须要用到氮氧化合物。

2)随着器件尺寸的缩放,工作电压并不随着物理尺寸的缩小而降低,导致作用于器件上的电场应力增大。小尺寸PMOS晶体管中会有更大的NBTI诱导的VT失配,尤其是SRAM。

NBTI测试通常在测试结构(test key)上进行而不是产品(芯片)上进行,且是在直流偏置条件下进行,因此计算出的寿命应被视为工艺或技术比较的品质因数。短的直流NBTI“寿命”并不意味着在交流条件下产品性能不可接受。

栅极诱导漏极泄漏(Gate-Induced-Drain-Leakage,GIDL)可能会由于负偏压温度不稳定性(NBTI)而增加(尤其是氮氧化合物比纯硅氧化物对NBTI更敏感),这是由于在栅极-漏极重叠区域的空穴损伤所致。通常,NBTI退化导致芯片电路速度降低而不是灾难性故障;当速度降低足够大讲导致芯片电路故障。另外,允许大电压过冲的电路可能对NBTI更敏感,因为电压越大栅极电压加速较大。

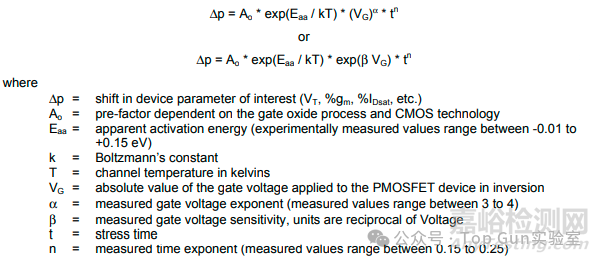

NBTI退化模型可以使用如下两个公式进行预估:

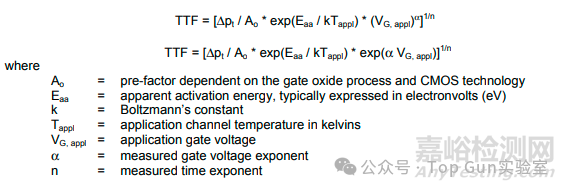

当规定的Δp退化至失效判据(Δpt)时,计算失效时间(TTF),对应上面两个退化模型公式:

注:失效判据Δpt 是根据允许的PMOS参数偏移量(例如ΔVT或%IDsat)来定义的。通常,失效判据的来源是芯片电路功能对PMOS参数敏感性以及对PMOS参数的要求。

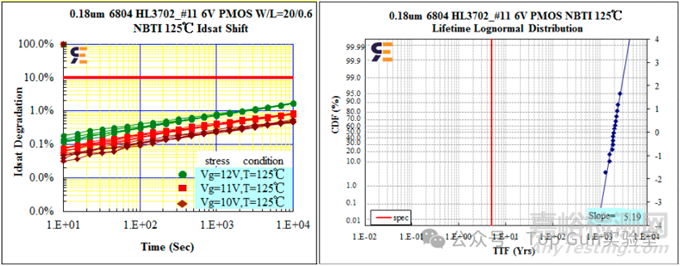

NBTI模式寿命预估示例:

目标:

计算加速因子(AF),即AF=TTFuse/TTFaccel

假设条件:

1)正常使用条件为:50°C芯片温度和VG=-1.0V

2)加速条件为:140°C和VG=-1.5V

3)α值为3.5

4)n值为0.25

5)表观活化能Eaa:-0.02eV

AF计算公式:

AF=(VG,accel/VG,use)α/n*exp[(Eaa/k)(1/Taccel–1/Tuse)(1/n)]

假设条件代入计算:

AF=[(1.5V/1V)3.5/0.25]*exp[(-0.02eV/8.62x10–5eV/K)(1/(273+140)K–1/(273+50)K)(1/0.25)]

AF=292*1.87=546

结论:从加速应力条件转变到正常使用条件,TTF值将增加到加速应力值的 546倍。

针对NBTI退化机制,下面列举了相关制程对NBTI的影响:

第一,氢是硅氢键的主要成键物质并在NBTI中起主要作用,氘是氢的同位素,与硅结合形成Si-D键,结合更强烈,具有更好的抗NBTI能力,在氮氢混合气体退火中采用D2而不是H2退火;

第二,栅氧中的水增强了NBTI效应,湿氧中的NBTI效应明显地要大于在干氧中的NBTI效应,通过在器件有源区覆盖SiN薄膜可以抑制水扩散进栅氧;

第三,栅氧化层氮化工艺的优化以平衡NBTI效应和硼穿通现象;

第四,氟对于MOS器件有很多有益效应,已知的有提高热载流子免疫力,氧化层完整性和NBTI效应;

第五,硼会增强NBTI效应,硼在S/D退火时穿进栅氧化层中。

第六,氧化层的损伤会增强NBTI效应,NBTI的好坏与栅极材料没有关联性,栅的预清洗动作对NBTI的效应有潜在影响,NBTI对于硅晶格方位有很强的敏感性;

第七,机械应力如去除保护层或者靠近STI处对器件的NBTI敏感性有影响,后段金属工艺对于NBTI也有很大影响,如水汽,PID等引起的器件退化。

附:NBTI测试与仿真

相关文献:

1)Blat, C.E., Nicollian, E.H., and Poindexter, E.H., “Mechanism of negative-bias-temperature instability,” Journal of Applied Physics, Vol. 69, Issue 3, 1991, pp. 1712-1720.

2)Alam, M.A. and Mahapatra, S., “A comprehensive model of PMOS NBTI degradation,” Microelectronics Reliability, Vol. 45, 2005, p. 71.

3)Huard, V., Denais, M., Perrier, F., Revil, N., Parthasarathy, C., Bravaix, A., and Vincent, E., “A thorough investigation of MOSFETs NBTI degradation,” Microelectronics Reliability, Vol. 45, 2005, pp. 83-98.

4)Mahapatra, S. and Alam, M.A., “A predictive reliability model for PMOS bias temperature degradation,” IEEE Technical Digest – International Electron Devices Meeting, 2002, pp. 505- 508.

5)Chakravarthi, S., Krishnan, A.T., Reddy, K, Machala, C.F., and Krishnan, S., “A comprehensive framework for predictive modeling of negative bias temperature instability,” IEEE International Reliability Physics Symposium Proceedings, 2004, pp. 273-282.

6)Krishnan, A.T., Reddy, V., Chakravarthi, S., Rodriguez, J., John, S., and Krishnan, S., “NBTI Impact on Transistor & Circuit: Models, Mechanisms & Scaling Effects,” IEEE Technical Digest – International Electron Devices Meeting, 2003, pp. 349-353.

7)Liu, C.H., Lee, M.T., Lin, C.Y., et al., “Mechanism and process dependence of negative bias temperature instability (NBTI) for pMOSFETs with ultrathin gate dielectrics,” IEEE Technical Digest – International Electron Devices Meeting, 2001, pp. 861-864.

8)Ershov, M., R. Lindley, R., S. Saxena, et al., “Transient effects and characterization methodology of negative bias temperature instability in PMOS transistors,” IEEE International Reliability Physics Symposium Proceedings, 2003, pp. 606-607.

9)Abadeer, W. and Ellis, W., “Behavior of NBTI under AC dynamic circuit conditions,” IEEE International Reliability Physics Symposium Proceedings, 2003, pp. 17-22.

10)Chen, G., Chuah, K.Y., Li, M.F., et al., “Dynamic NBTI of PMOS transistors and its Impact on MOSFET lifetime,” IEEE International Reliability Physics Symposium Proceedings, 2003, pp. 196-202.

11)Krishnan, A.T., Reddy, V., and Krishnan, S., “Impact of charging damage on negative bias temperature instability,” IEEE Technical Digest – International Electron Devices Meeting, 2001, pp. 865-868.

12)Mahapatra, S., Ahmed, K., Varghese, D., Islam, A.E., Gupta, G., Madhav, L., Saha, D., and Alam, M.A., “On the physical mechanism of NBTI in silicon oxynitride p-MOSFETs: Can differences in insulator processing conditions resolve the interface trap generation versus hole trapping controversy?,” IEEE International Reliability Physics Symposium Proceedings, 2007, pp. 1-9.

来源:Top Gun实验室