您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2024-10-16 09:31

闩锁效应存在于体CMOS集成电路中,它一直是CMOS集成电路可靠性的一个潜在的严重问题,随着CMOS技术的不断发展,器件的尺寸越来越小,同时器件间的间距也越来越小,集成电路的器件密度越来越大,集成电路的闩锁效应变得越来越严重,特别是在输入输出电路。

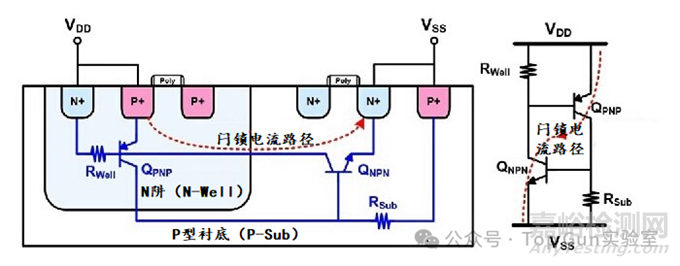

在CMOS集成电路中,形成MOS晶体管的同时也会形成相应的寄生双极晶体管结构。在PMOS中,源和漏的重掺杂p+型有源区,N阱(N-Well)扩散区和P型衬底(P-sub)会形成纵向寄生的PNP结构;在NMOS中,源和漏的重掺杂n+型有源区,P阱(P-Well)扩散区和PMOS的N阱扩散区会形成横向寄生的NPN结构。在正常情况下,寄生的BJT都是截止的;当其中一个BJT的集电极电流受外部干扰突然增加到一定值时,该BJT的发射结正偏,电流反馈到另一个BJT,从而使两个BJT因触发而导通进入闩锁状态。图1是典型CMOS器件剖面图及其寄生效应等效电路图。

图1 典型CMOS器件剖面图及其寄生效应等效电路图

在正常情况下,这些寄生双极晶体管都是截止的,即高阻阻塞态,寄生双极晶体管组成的电路在高阻阻塞态下,它们具有很高的阻抗,漏电流非常小。但是在一定的触发条件下,寄生双极晶体管组成的电路会被触发进入低阻闩锁态。

如果触发条件去除后,这些寄生的双极晶体管仍然能保持低阻闩锁态,那么此时低阻闩锁态是可持续的,电压信号足以维持低阻闩锁态,把这种现象称为自持,自持就是一旦两个寄生双极晶体管导通后,在VDD和VSS之间形成低阻通路形成大电流,并且产生正反馈回路使两个寄生双极晶体管一直导通,电路在电源VDD和地VSS之间一直保持低阻通路;如果触发条件去除后,寄生双极晶体管从低阻闩锁态恢复到高阻阻塞态,那么低阻闩锁态是暂时的不可持续的,电压信号不足以维持低阻闩锁态,寄生双极晶体管组成的电路不具有自持能力。

闩锁效应的发生的条件:

1)QNPN和QPNP寄生BJT都导通,在VDD和VSS之间产生低阻抗通路,详见图1红色虚线;

2)两个晶体管反馈回路增益的乘积大于1(β1×β2≥1),β1为QPNP的基极到集电极的电流增益,β2为QNPN的基极到集电极的电流增益。

注:从传输线脉冲TLP(TransmissionLine Pulse)I-V曲线的角度解释闩锁效应会更清晰,有兴趣的同学可以搜索学习。

当电路一旦发生闩锁效应,可能形成大电流,假如没有限流机制,低阻闩锁态产生大电流可能将PN结或者铝线烧毁,因此就算低阻闩锁态是暂时的,如果没有限流机制,也会造成电路永久失效,这种情况也可以认为电路发生了闩锁效应。所以闩锁效应具有两种形式:一种是具有自持能力的闩锁效应,此时无论闩锁效应有没有造成芯片损毁,它都会导致CMOS芯片无法正常工作;第二种是不具有自持能力的闩锁效应,低阻闩锁态只是暂时的,但是此时的低阻闩锁态会产生大电流烧毁芯片,它也闩锁效应的一种形式。闩锁效应最易发生在易受外部干扰的输入输出电路,也偶尔发生在内部电路;闩锁有时会导致芯片烧毁,有时解除闩锁条件后又能恢复正常(主要看电路有没有限流,造成芯片永久性失效的通常为热失效)。

发生闩锁的常见条件:

1)输入输出电路发生闩锁的原因一般是输入或输出引脚信号的上冲/下冲;

2)内部电路发生闩锁的原因一般是芯片在高温条件下寄生双极晶体管漏电流过大触发闩锁条件发生自持。

来源: Top Gun实验室