您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2024-10-20 11:54

各阶段常见的典型失效机理

前段制程(FEoL)常见的失效机理

1)与时间相关的电介质击穿(TDDB)-- 栅极氧化物

2)热载流子注入(HCI)

3)负偏压温度不稳定性(NBTI)

4)表面反转(移动离子)

5)浮栅非易失性存储器数据保持

6)局部电荷捕获非易失性存储器数据保持

7)相变(PCM)非易失性存储器数据保持

后段制程(BEoL)常见的失效机理

1)与时间相关的电介质击穿(TDDB)-- 层间电介质/低k值/移动铜离子

2)铝电迁移(Al EM)

3)铜电迁移(Cu EM)

4)铝和铜腐蚀

5)铝应力迁移(Al SM)

6)铜应力迁移(Cu SM)

封装/界面常见的失效机理

1)因温度循环和热冲击导致的疲劳失效

2)因温度循环和热冲击导致的界面失效

3)因高温导致的金属间化合物和氧化失效

4)锡须

5)离子迁移动力学(PCB)--组件清洁度

本文对FEoL阶段的局部电荷捕获非易失性存储器数据保持模型进行研究

在局部电荷捕获型非易失性存储(NVM)器件中(如NROM),一个单元的阈值电压(VT)由在n沟道MOSFET晶体管结边缘的ONO(氧化物-氮化物-氧化物)介电层中捕获的电荷量和空间分布所决定。通常,NVM通过沟道热电子注入进行编程,通过沟道热空穴辅助隧穿进行擦除。电荷从晶体管的n沟道通过3~6nm厚的下层氧化物层注入到ONO结构的氮化物层中,电荷存储在结边缘附近。典型结构如下图所示。

凭借氮化物的高介电常数,ONO有助于确保浮栅中的电荷保留,数据保留可靠性取决于ONO层保留捕获电荷的能力。NROM器件数据保留可靠性的主要影响因素是捕获电荷的迁移,电荷迁移会影响NROM单元的VT。下层氧化物厚度大于4nm的NROM技术对垂直电荷损失相对免疫,底部介电层中的点缺陷(SILC型泄漏)只会导致极小部分存储电荷的损失。

退化模型研究

无偏压NVM退化模型是一个由时间、温度和编程/擦除次数组成的函数。该模型描述了已编程NROM单元的VT降低情况,已编程的NROM单元VT的降低归因于在器件结边缘循环期间积累的空穴的迁移。在长期存储期间或在高温烘烤条件下,这些空穴脱陷并横向向在沟道上更远位置捕获的电子迁移,抵消它们的电场,降低NROM单元的VT。

注:该模型适用于两种类型的电荷载体都已注入的单元,由于空穴和电子的注入条件和微观散射机制不同,预计介电层中捕获的空穴和捕获的电子的空间分布会略有不同,从而导致内部横向偶极子(多极子)的产生。氮化物中的电子相对不移动,几乎不参与电荷迁移过程。

氮化物薄膜中空穴的横向迁移动力学遵循分散传输机制,该机制涉及载流子多次地捕获和脱陷,随着载流子从一个陷阱落入下一个陷阱,释放时间随机增加(与时间相关的扩散系数和拉伸指数动力学)。

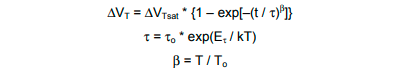

相对于其初始编程状态,阈值电压随时间的变化ΔVT由以下公式描述:

其中,ΔVTsat是数据保留退化的饱和值,t是存储时间,T是的存储温度(开尔文),τ是时间常数,Eτ是偶极弛豫过程的特征能量,k是玻尔兹曼常数,τo和To是经验系数。参数ΔVTsat、τo和Eτ取决于产品、工艺和编程/擦除次数。无论晶圆厂或技术节点如何,所有NROM产品的To系数的值均为2550±100K。

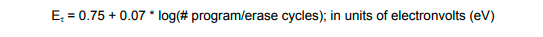

表观活化能根据编程/擦除次数的公式如下:

饱和值 ΔVTsat 的大小取决于循环次数,饱和的定义是横向迁移停止,原因是用于迁移的有限数量的过量空穴已与电子复合或已达到稳态。在空穴迁移停止后,沟道上方剩余的电子决定了烘烤后的剩余VT。

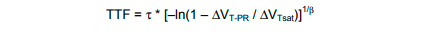

我们用ΔVT-PR表示一组已编程位中最低位的VT(通常称为编程验证电平)与关键参考读取电平的VT之间的差值。ΔVT-PR是产品定制参数,VT降低ΔVT-PR所需的时间就是失效时间(TTF)。TTF为方程为:

TTF与编程/擦除次数的相关性通过ΔVTsat与编程/擦除次数的幂次相关性体现,而TTF与温度的相关性通过参数τ和β与温度的相关性体现。

正常使用条件下的TTF除以高温应力下的FFT,获得加速因子AF:

局部电荷捕获非易失性存储器数据保持寿命预估示例:

目标:

1)计算加速因子(AF)。

2)在100,000次循环后,保证芯片在50°C下达到5年数据保持所需的加速应力时间。

假设条件:

1)正常使用条件为:50°C芯片温度。

2)加速鉴定条件为:125℃。

3)活化能,Eτ:100,000次循环后,1.1eV

4)假设对于选定的工艺和产品,ΔVTsat(100,000次循环)=1.6V,并且该产品设计的编程余量为ΔVT-PR=1.0 V。

AF计算公式:

AF=exp[(Eτ/k)(1/Tuse–1/Tstress)]*[–ln(1–ΔVT-PR/ΔVTsat)](1/βuse–1/βstress)

AF=exp[(1.1eV/8.62x10–5eV/K)(1/(273+50)K–1/ (273+125)K)]*1=1711

注:–ln(1–1V/1.6V)≈1

因此:TTFstress=TTFuse/AF=5years/1711=25.6hours

结论:

要使产品在10万次编程/擦除循环后在正常使用条件下达到5年的数据保持的要求,那么该产品必须在10万次编程/擦除循环后能够承受住125°C烘烤25.6小时数据不丢失。

参考文献:

1)M. Janai, B. Eitan, A. Shappir, E. Lusky, I. Bloom, and G. Cohen, “Data retention reliability model of NROM nonvolatile memory products,” IEEE Transactions on Device and Materials Reliability, Vol. 4, Issue 3, 2004, pp. 404-415.

2)M. Janai and B. Eitan, “The Kinetics of Degradation of Data Retention of Post-Cycled NROM Non-Volatile Memory Products,” IEEE International Reliability Physics Symposium Proceedings, 2005, pp. 175-180.

3)E. Lusky, Y. Shacham-Diamand, I. Bloom, and B. Eitan, “Electrons Retention Model for Localized Charge in Oxide–Nitride–Oxide (ONO) Dielectric,” IEEE Electron Device Letters, Vol. 23, Issue 9, 2002, pp. 556-558.

来源:Top Gun实验室