您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2024-11-19 11:56

芯片对更高速度的持续需求迫使越来越多的能量流经越来越小的器件,这增加了电流密度,并威胁到芯片的长期可靠性。虽然这一问题已被广泛理解,但在尖端器件设计中,这种问题越来越难以解决。

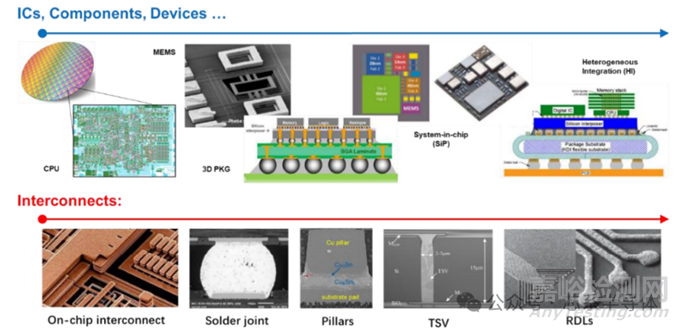

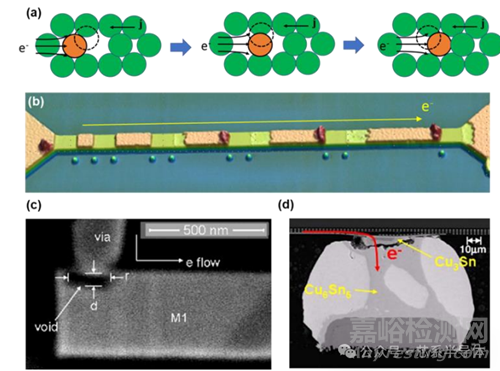

特别值得关注的是*电迁移*问题。在使用多个小芯片(chiplets)的先进封装中,这一问题愈发严重。在这些封装中,各种键合和互连方案导致材料和几何结构发生突变。例如,电子可能从铜导线移动到SAC(锡-银-铜)焊点,再到基于镍的凸点下金属(underbump metal),最后到中介层的铜垫上。这可能导致原子发生迁移,从而导致焊点或高密度扇出封装中的铜重分布层发生故障。

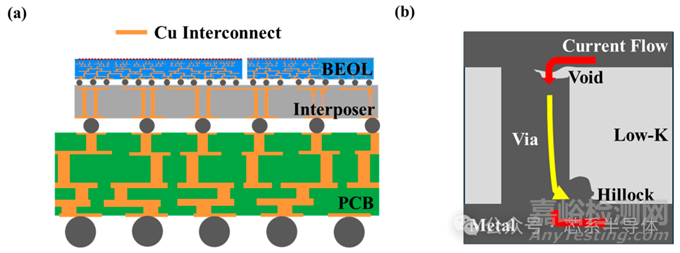

电迁移(Electromigration)是由于导体(通常为铜)中电流流动产生的“电子风”导致金属原子迁移的现象。当电流密度足够高时,金属会沿电流方向扩散,在下游形成微小的凸起,同时留下空隙或孔洞。当电迁移足够严重时,会导致以下两种失效形式:一是由于导线的严重变薄导致断路(开路),二是由于凸起桥接相邻导线导致短路。电迁移是一种扩散控制的机制,可以表现为三种形式——体扩散、晶界扩散或表面扩散,具体取决于金属的性质。例如,铝主要通过晶界扩散迁移,而铜则倾向于在表面或晶界上迁移。

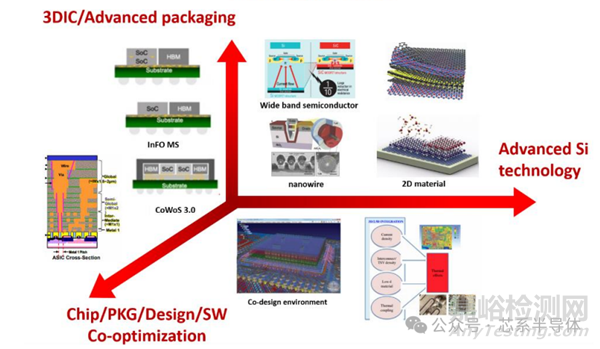

在半导体行业的大部分历史中,电迁移主要是一个芯片内问题,但得益于可靠性工程师的努力,芯片内电迁移的问题已基本得到控制。然而,随着先进封装技术的迅速发展(包括硅通孔(TSV)、具有重分布层(RDL)的扇出封装以及铜柱凸点的应用),电迁移已成为封装层面上的主要威胁。先进封装导致封装密度增加、封装尺寸减小,同时互连结构的尺寸也在缩小,因此电流密度现在非常接近每个电迁移设计规则规定的最大电流密度限制。

在封装装配和使用过程中,任何可能施加的额外应力(无论是机械应力还是热应力)都会诱发或加速电迁移。总体来说,电迁移由于温度和应力的影响会变得更糟,而这两点在先进封装中都得到了强化。电迁移是累积性的,也就是说它会整合芯片整个生命周期内的所有高温和应力,直到某一互连结构出现断裂或短路。更高的加工温度和运行温度会加剧这一问题,但它的严重程度也取决于在这些温度下的持续时间。

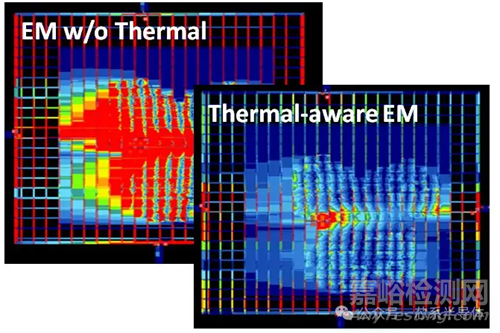

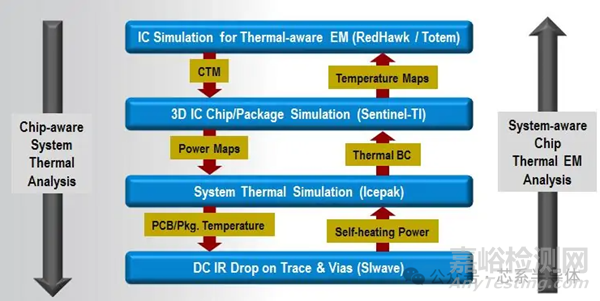

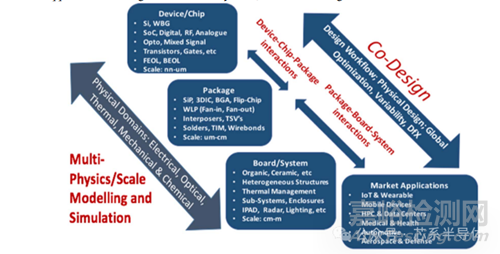

事实上,*热通道*可能是通往终极封装——3D-IC的过程中面临的最大挑战之一。电迁移对温度非常敏感,根据热分布图,电源完整性必须适应你的局部温度分布。当你查看一块芯片时,可以计算出它消耗了多少功率,但你无法准确预测芯片会有多热,因为‘这取决于很多因素’。比如它是放在冷板上,还是暴露在撒哈拉的阳光下?这些都涉及系统性问题,因此多物理场建模对理解这些相互依赖的效应非常重要。

热工程还包括将热量从最易失效的点(如焊点)移开。有效的热管理对焊点的可靠性至关重要,工程师们正在采用热界面材料和先进的散热解决方案等热增强技术,以确保焊点不会承受过度的温度相关应力。工程师们正在研究新材料,同时优化现有材料的使用,以尽量减少电迁移的可能性。半导体封装工程师正在实施一系列措施,以提高焊点的可靠性并最大化焊点的产量。这些策略包括开发用于焊点和凸点下金属的新材料,优化焊点的尺寸、间距和形状以提高可靠性,采用先进的工艺控制方法以减少变异并最大化产量,以及对可靠性进行模拟和建模。

需要特别注意的是,电迁移是一个*失控的过程*。随着电流密度或温度的增加,电迁移加剧,从而提高电流密度,导致更多金属迁移,形成破坏性的反馈循环。

电迁移失效模式与允许电流密度

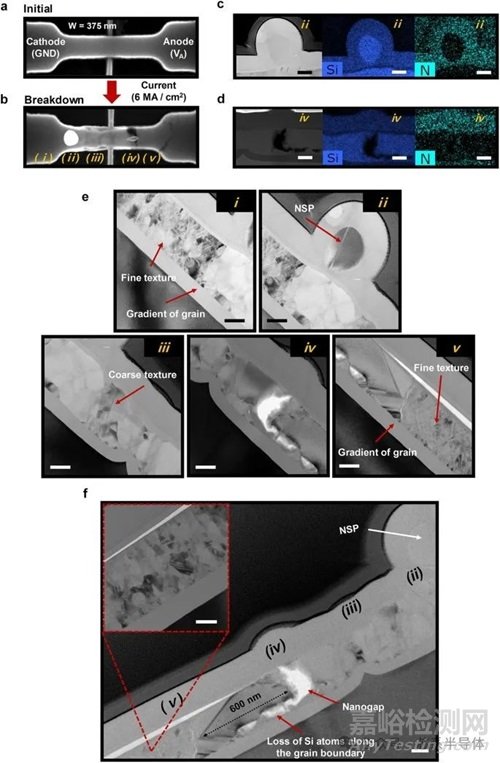

在聚酰亚胺材料中的铜重分布层(RDL)内,当电流通过RDL时,由于焦耳热的产生,导体中的热量会积累,影响性能。当精细线条的铜RDL结构(<5nm线宽和间距)的所需电流密度和焦耳热温度增加时,自发热被认为是高密度扇出封装可靠性的重要因素。

高密度扇出技术是一种新兴技术,其缩放比比晶圆级扇出封装更激进。通过钽/铜种子层制备的3µm厚三层铜RDL被填充聚酰亚胺、铜柱沉积、芯片粘合和塑封。Kwon团队在不同的电流密度和温度下测试了2µm和10µm RDL,直到电阻增加100%(表示EM失效),但允许的最大电流密度对应于电阻增加20%。失效模式分为两个阶段:首先是孔洞的形成与生长,其次是铜的还原和氧化。确定激活能(Ea)和电流密度指数值,这些结果对未来RDL设计具有指导意义。

与此同时,ASE研究团队最近演示了如何评估电迁移对高功率汽车应用中倒装芯片四方扁平无引脚(FCQFN)封装中铜柱互连的影响。这种多层铜柱焊点具有Cu/Ni/Sn1.8Ag配置,与镀银铜引线框架键合,并在10 kA/cm²电流密度和150°C、160°C、180°C温度的极端电迁移条件下进行了*原位电阻测量*。

实验显示,电迁移失效与Cu/焊料界面的金属间化合物和孔洞的形成有关,表现为电阻的快速上升。研究团队基于Black型EM方程并遵循JEDEC标准,建立了互连结构的EM预测模型,并设计了五种测试条件。

通过对样品寿命的统计计算,ASE团队确定了FCQFN封装中铜柱互连的激活能为*1.12 ± 0.03 eV*。在*105°C工作温度*下,以0.1%失效率持续10年的铜柱互连最大允许电流为*2A以上*。

电迁移设计与制造抗性

在先进器件中构建电迁移抗性,首先需要在电路设计中仅使用符合电迁移要求的线宽。这种设计需要基于互连结构在设备生命周期中经历的电流密度和热分布情况。电迁移的缓解还要求在工艺和材料工程方面确保耐用性,例如BGA封装下铜柱焊点的耐久性。同时,还需要优化装配工艺窗口并实施严格的工艺控制,以防止设计规则的细微违规,这些违规可能在后续发展为电迁移失效。

随着行业逐步迈向真正的*3D封装*,并最终实现*3DIC*,建模与仿真工具在制造和装配开始前,确定许多关键制造规范方面的作用显得日益重要。可靠性建模与仿真工具正在用于更好地理解焊点结构的可靠性,这种主动的方法有助于在问题出现之前识别潜在问题,从而使工程师能够实施预防措施。在系统层面进行建模和仿真也将变得至关重要,以便理解多芯片系统在运行期间可靠性机制与热、机械应力之间的复杂相互作用。

对于堆叠芯片的电迁移而言,这是一个巨大的挑战,局部的芯片间负载会导致特定区域的重复电流流动。这会产生局部热量,增加电迁移的可能性,从而导致导线退化并产生更多热量。因此,降低热量问题对于确保电迁移的可靠性至关重要。如前所述,焊点可能成为电迁移可靠性失效的热点。工程师们从焊点的尺寸、间距和形状等方面精确优化设计,以确保整个封装的一致性和可靠性。这还包括采用创新的铜焊点结构,以改善机械和电气性能。

在倒装芯片BGA和其他倒装芯片应用中,通常使用热固性环氧树脂作为底填材料,以减少焊点上的热应力。底填材料在为焊点提供机械支撑和热稳定性方面起着关键作用,工程师们正在开发具有改进性能的先进底填配方,例如改善的粘附性、导热性和应力缓解能力。

总结

由于电迁移对温度的依赖性,随着器件的持续缩放和系统集成商在先进封装中不断增加不同功能的小芯片,电迁移成为必须关注和规划的重要失效机制。在先进技术中,电流密度现在已经非常接近最大允许密度,任何会导致温度升高的因素都构成威胁。多芯片系统的设计者需要理解温度的影响并设计出能够散热的系统。

References

JiHye Kwon, “Electromigration Performance Of Fine-Line Cu Redistribution Layer (RDL) For HDFO Packaging,” Semiconductor Engineering, Jan. 18, 2024, https://semiengineering.com/electromigration-performance-of-fine-line-cu-redistribution-layer-rdl-for-hdfo-packaging/

-Y. Tsai, et al., “An Electromigration Study of Cu Pillar Interconnects in Flip-chip QFN Packaging under Extreme Conditions for High-power Applications,” 2023 IEEE 25th Electronics Packaging Technology Conference (EPTC), Singapore, 2023, pp. 326-332, doi: 10.1109/EPTC59621.2023.10457564.

https://www.nature.com/articles/srep19314

https://www.mdpi.com/2072-666X/15/10/1207

https://semiwiki.com/eda/ansys-inc/4220-ansys-talks-about-multi-physics-for-thermal-analysis-at-designcon/

https://pure.tudelft.nl/ws/portalfiles/portal/103011287/PhD_dissertation_Zhen_Cui.pdf

https://eps.ieee.org/images/files/HIR_2021/ch14_sim.pdf

来源:芯系半导体