您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2024-12-07 15:16

(1)量子物理效应制约摩尔定律正常延续

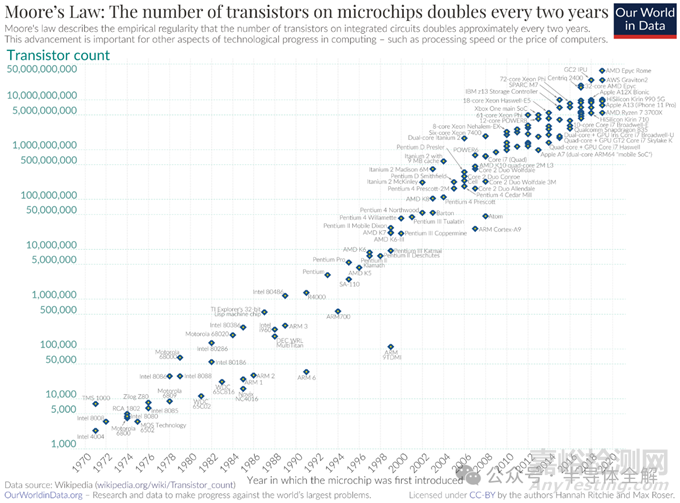

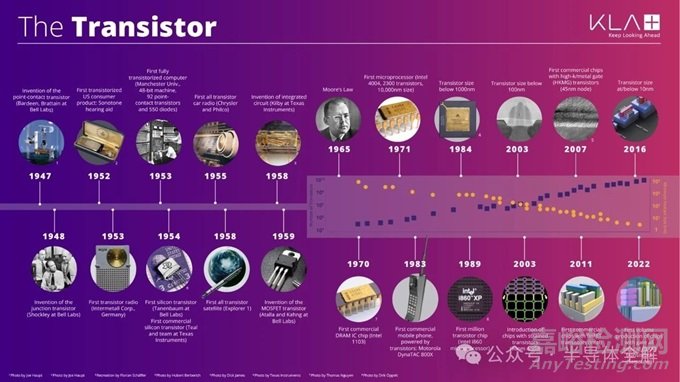

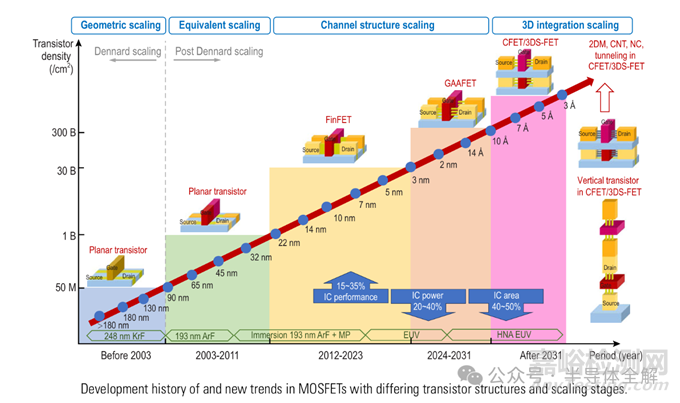

最近半个多世纪信息技术的高速发展很大程度上可以归因于摩尔定律的持续。摩尔定律是英特尔创始人之一的戈登·摩尔于1965年提出经验规律,其指出集成电路上可以容纳的晶体管数目在大约每经过18个月到24个月便会增加一倍,即处理器的性能大约每两年翻一倍,同时价格下降为之前的一半。

近几十年来摩尔定律的延续带来了算力的指数级增长、生产效率的极大提高以及人类生活形态的根本变化。但是,遵循摩尔定律的芯片技术发展不可永久持续。随着半导体制程节点的持续演进,短沟道效应以及量子隧穿效应带来的发热、漏电等问题愈发严重,对缩微器件的性能产生由量到质的影响,追求经济效能的摩尔定律日趋放缓,难以为继。

目前集成电路行业已经进入到了后摩尔时代,为保障芯片性能的不断提升,身处后摩尔时代需要进一步发展新理论和新技术来延续摩尔定律(More Moore)或超越摩尔定律(More than Moore)。

延续摩尔定律主要是指在晶体管结构优化和工艺微缩方向继续挖掘,超越摩尔定律则是转向探索系统级架构优化,新材料替换,制造方法和算法优化等。

摩尔定律继续推进所带来的经济效益正在锐减。随着先进工艺节点不断演进,芯片的线宽不断缩小,单颗芯片上可容纳的晶体管数量也快速增加,单位面积性能得以相应提升。根据IBS报告,以80mm²面积的芯片裸片为例,在16nm工艺节点下,单颗裸片可容纳的晶体管数量为21.12亿个;在7nm工艺节点下,该晶体管数量可增长到69.68亿个。单位面积下晶体管数量的快速上升促使晶体管的单位成本快速下降。

当芯片制程进一步接近1nm时,量子物理的影响将非常显著,现有工艺制程会受到量子效应的极大影响,因此很难进一步往前推进。除此之外,新工艺制程也带来了极其昂贵的研发成本。

(2)新型器件结构暂缓摩尔定律失效。

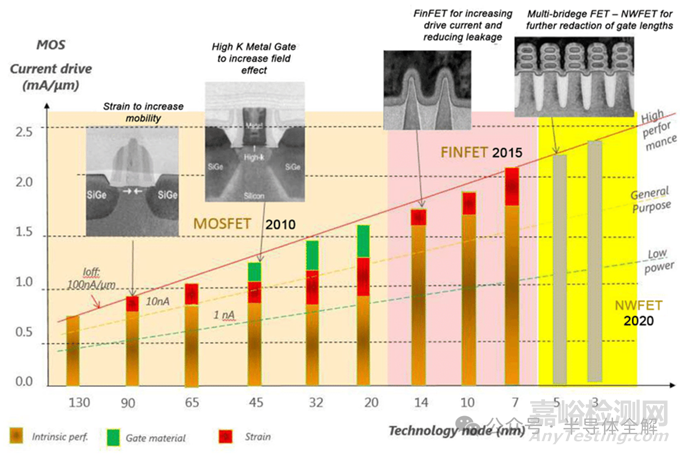

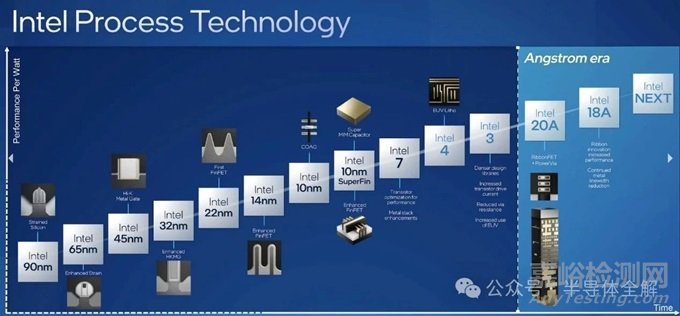

在45nm工艺制程之前摩尔定律基本可以正常延续,而到了45nm工艺节点时,过大的泄漏电流已经让微缩难以为继,因此英特尔采用了被称为high-k的崭新材料来制造晶体管闸极电介质,晶体管闸极的电极也采用了新的金属材料组合。

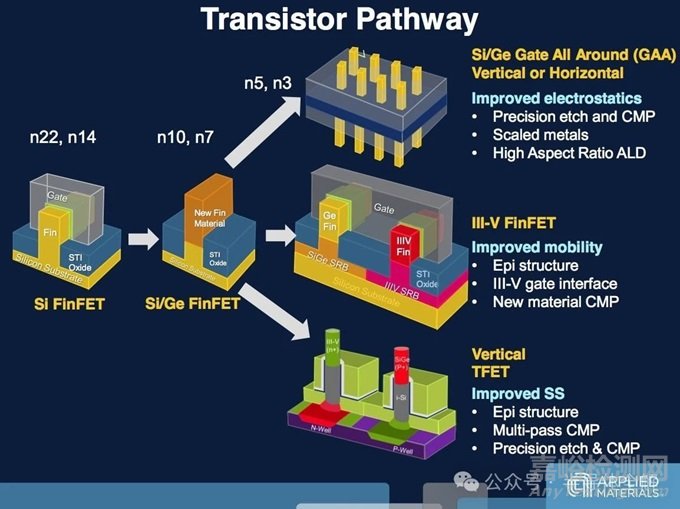

而当工艺制程进一步演进到28nm以下时,传统的平面晶体管结构完全不能支撑进一步器件微缩,2011年以后以FinFET为代表的新型器件结构全面崛起帮助了摩尔定律的延续。至此以后工艺制程的微缩变得更为困难,英特尔公司的制程也长期被卡在14nm附近导致处理器性能提升缓慢。即便是采用了FinFET技术也并没有能够为摩尔定律延寿多久,随着工艺制程进入了10nm以下,一些如GAAFET这样的新的器件结构又将被应用到产业中。

(3)FinFET成为半导体器件主流选择。

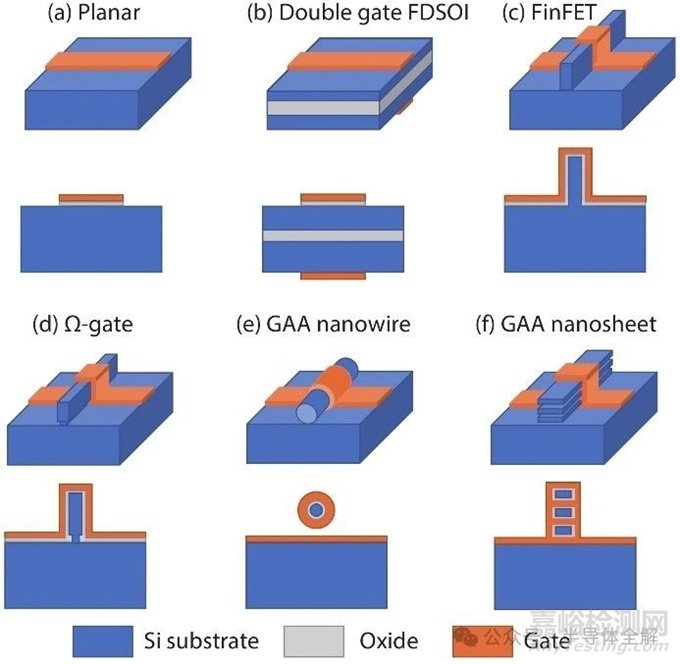

从1960年到2010年左右,基本的平面MOSFET(PlanarFET)结构基本保持不变,直到进一步增加晶体管密度和降低器件功耗变得不可能。加州大学伯克利分校的胡正明教授在1999年报道了平面晶体管的后继者FinFET的发明,在三维结构的MOS晶体管与双栅MOSFET结构的基础上进一步提出了自对准的双栅MOSFET结构,因为该晶体管的形状类似鱼鳍,所以称为FinFET晶体管(鳍式场效应晶体管)。

FinFET作为第一个3DMOSFET,将扁平而宽的晶体管结构变为高而窄的晶体管结构,其好处是在更小的面积内获得更好的性能,可以类比为在拥挤的城市中多层建筑相对于单层建筑的优势。

从结构来看,平面MOSFET只能在闸门的一侧控制电路的接通与断开,但是在FinFET架构中,闸门被设计成类似鱼鳍的叉状3D架构,可于电路的两侧控制电路的接通与断开。这种叉状3D架构不仅能改善电路控制和减少漏电流,同时让晶体管的闸长大幅度缩减。英特尔在FinFET工艺上率先推进,于2011年推出商业化FinFET技术并应用到22nm制程工艺上,显著提高性能的同时降低了功耗。之后台积电、三星等全球各大厂商陆续跟进,在16/14nm节点中采用FinFET技术并取得了巨大成功,使得FinFET大放异彩。

GAAFET工艺接力FinFET实现更高效晶体管设计。从16/14nm开始,FinFET已经成为半导体器件的主流选择,成功推动了数代半导体工艺的发展,不过FinFET工艺的物理极限是7nm制程。到了7nm节点后即使是FinFET也不足以在保证性能的同时抑制漏电,但是在极紫外(EUV)光刻机以及砷化铟镓的助力下,FinFET得以在7nm以下的更先进制程中使用。到了5nm节点后,虽然已经使用上了EUV光刻技术,但是基于FinFET结构进行的芯片尺寸缩小也出现了诸多问题,变得更加困难。鳍片距离太近、漏电重新出现,再加上其不断拉高的深度和宽度之比将使得鳍片难以在本身材料内部应力的作用下维持直立形态,以及物理材料的极限都让3DFinFET晶体管难以为继。FinFET走向极限时,延续半导体技术经典摩尔定律的新兴技术GAAFET问世,其中环栅(GAA)是一种新的3D薄体CMOS结构。GAAFET工艺围绕通道的四个侧面设计,以确保减少功率的泄漏,进一步改善对通道的控制。

此外,GAAFET工艺还能够实现更高效的晶体管设计,拥有更小的整体制程尺寸,大大提升了芯片的每瓦性能。

GAAFET有两种结构:使用纳米线(Nanowire)作为电子晶体管鳍片的常见GAAFET;与以纳米片(Nanosheet)形式出现的较厚鳍片的多桥通道场效应管MBCFET,这两种方式都可以实现3nm工艺节点。从GAAFET到MBCFET,可以视为从二维到三维的拓展,能够有效改进电路控制,降低漏电率。

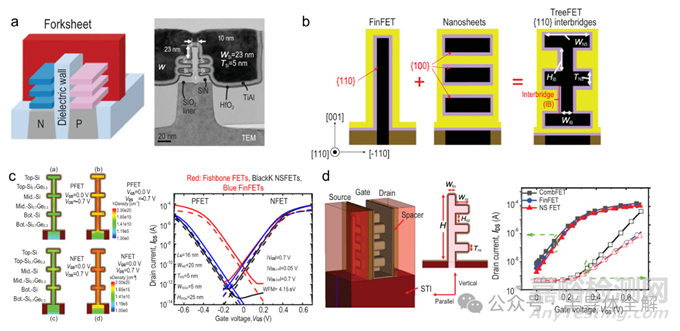

CFET有望助力突破1nm工艺节点。为了进一步加强静电控制能力,CFET(Complementary FET,互补场效应晶体管)也随即诞生,这是一种新型三维结构晶体管工艺,它在GAAFET工艺基础上改进得到。

CFET一般采用Nanosheet结构,将一个p型NanosheetFET叠加在一个n型Nanosheet FET之上实现工艺单元集成,减少单个工艺单元的面积占用,形成三维晶体管。CFET在4T(Track)轨道单元设计中优于叉片晶体管,使其成为1nm以下逻辑技术节点中极具吸引力的器件架构。

但值得说明的是CFET的标准单元(standard cell)设计要求从全局考虑以克服堆叠结构带来的高度限制,以便实现对晶体管性能最大化增益。

FinFET、GAA、CFET等工艺从晶体管结构优化方向有效延续了摩尔定律,但这些新型器件的结构导致工艺复杂,各大厂商实现的技术路线也各不相同。例如同样是7nm制程的,台积电和三星的采取的技术路线区别很大。目前摩尔定律的延续已经变得十分困难,大量新技术新工艺以及新结构的采用使得芯片制造成本成倍增加。为维持晶体管密度持续增加,每革新一代制程需要大量的技术和工艺创新,因而经济成本很难摊薄。此外随着晶体管的不断微缩,晶体管的缺陷问题也在不断增加,当前晶体管的加工无论是多重曝光还是浸润式光刻均是在追求极致的微缩,会大幅提升工艺一致性和准确性控制的难度,因此出现工艺误差甚至加工缺陷的情况愈发严重,最终导致芯片成品率低、器件故障率高,加工出来的合格产品价格居高不下,这也使得产业界需要在器件工艺之外探索更多样性的功能实现方法来超越摩尔定律。

来源:Internet