您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2021-02-09 08:41

目录

1、ESD概念

1.1、人体放电模式(Human-Body Model,HBM):

1.2、机器放电模式(Machine Model,MM)

1.3、元件充电模式(Charged-Device Model,CDM)

1.4、电场感应模式(Field-Induced Model,FIM)

2、静电放电标准

2.1、IEC-61000-4-2 or EN-61000-4-2 p.19

2.2、ESD Gun Model

2.2.2、国外教科书的(放电)模型

2.2.3、法规定义放电电流数学方程式(EN-61000-4-2 , P13)

3、静电放电模型

3.1、以两级RLC模拟身体(135~150pF)与手臂(12~15pF)的两波放电模型,输出端以V_Probe与I_Probe观察

3.2、从法规所提供的基本模型加上静电枪对地寄生RLC的放电模型

3.3、根据paper【4】【8】所建的ESD Gun等效模型

4. 采用ESD Gun Model进行产品EMC设计

4.1、采用Siwave快速设计PCB静电参数

4.2、ESD的频率分布

4.3、采用CST进行ESD分析

Reference

1、ESD概念

静电放电(Electorstatic Discharge,ESD)是造成大多数电子元件或电子系统收到过度电性应力破坏的主要因素。这种破坏会导致半导体元件以及电脑系统等,形成一种永久性破坏,因而影响积体电路的电路功能,而使得电子产品工作不正常。

根据ESD产生原因及对积体电路放电的方式,ESD目前被分为以下四类:

(1) 人体放电模式(Human-Body Model,HBM)

(2) 机器放电模式(Machine Model,MM)

(3) 元件充电模式(Charged-Device Model,CDM)

(4) 电场感应模式(Field-Induced Model,FIM)

1.1、人体放电模式(Human-Body Model,HBM):

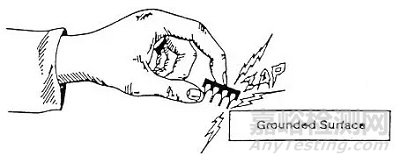

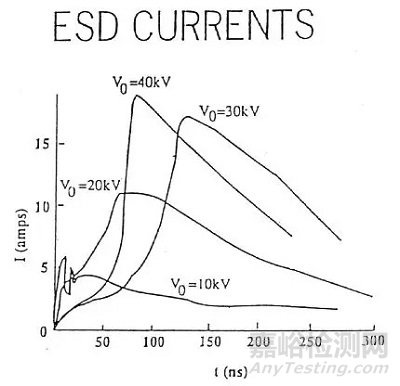

人体放电模式(HBM)的ESD是指因人体在地上走动摩擦或其他因素在人体上已积累了静电,当此人去触碰到IC时,人体上的静电便会经由IC的引脚而进入IC内,再经由IC放电到地去,如图1.a所示。此放电的过程会在短到几百纳秒的时间内产生数安培的瞬间放电电流,此电流会把IC内的元件烧毁。不同HBM静电电压相对产生的瞬间放电电流与实践的关系如图1.b。对一般商用IC的2KV ESD放电电压而言,其瞬间放电电流的尖峰值大约是1.33安培。

图1.aHBM的ESD发生情形

图1.b在不同HBM静电电压下,其静电放电电流随时间的变化

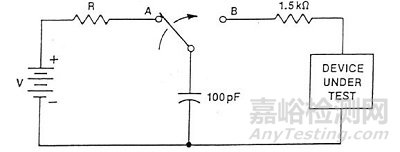

有关于HBM的ESD已有工业测试标准,为现今各国用来判断IC ESD可靠度的重要依据。图2表示此工业标准(MIL-STD-883C method 3015.7)的等效电路图,其中人体的等效电容为100pF,人体的等效放电电阻定为1.5KΩ。另外在国际电子工业标准(EIA/JEDEC STANDARD)中,也对此人体放电模式规定了测试规范(EIA/JESD22-A114-A)。

TestStandard : MIL-STD-883C Method 3015.7

|

CLASSIFICATION |

Sensitivity |

|

Class 1 |

0 to 1,999 Volts |

|

Class 2 |

2,000 to 3,999 Volts |

|

Class 3 |

4,000 to 15,999 Volts |

图2、人体放电模式(HBM)的工业标准测试等效电路及其耐压能力等级分类

1.2、机器放电模式(Machine Model,MM)

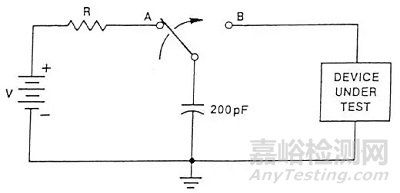

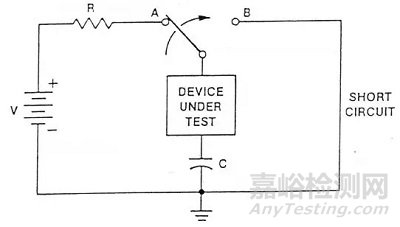

机器放电模式的ESD是指机器(例如机械手臂)本身积累了静电,当此机器去触碰到IC时,该静电便经由IC的pin放电。此机器放电模式的工业测试标准为EIAJ-IC-121 method 20,其等效电路如图3所示。

TestStandard : EIAJ-IC-121 Method 20

|

CLASS |

STRESS LEVELS |

|

M0 |

0 to <50V |

|

M1 |

50 to <100V |

|

M2 |

100 to <200V |

|

M3 |

200 to <400V |

|

M4 |

400 to <800V |

|

M5 |

>800V |

图3、机器放电模式(MM)的工业标准测试等效电路机器耐压能力等级分类

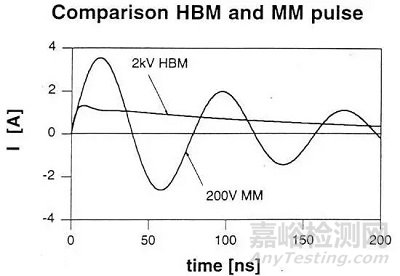

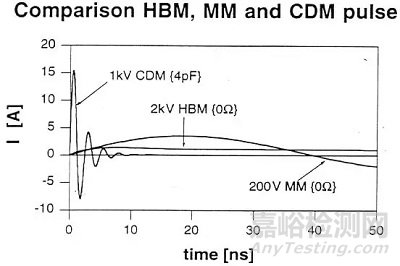

因为大多数机器都是用金属制造的,机器放电模式的等效电阻为0Ω,其等效电容定为200pF。由于机器放电模式的等效电阻为0,故其放电的过程更短,在几纳秒到几十纳秒之间会有数安培的瞬间放电电流产生。有关2KV HBM与200V MM的放电电流比较,在下图4中。

虽然HBM的电压2KV比MM的电压200V更大,但是200V MM的放电电流却比2KV HBM的放电电流大很多,因此机器放电模式对IC的破坏力更大。在图4中,该200V MM的放电电流波形有振铃的情形,是因为测试设备导线的杂散等效电感与电容互相耦合而引起的。

图4、人体放电模式(2KV)与机器放电模式(200V)放电电流的比较图

另外在国际电子工业标准(EIA/JEDECSTANDARD)中,也对此机器放电模式制定了测试规范(EIA/JESD22-A115-A),详情请参考具体标准。

1.3、元件充电模式(Charged-Device Model,CDM)

此放电模式是指IC先因摩擦或其他因素在IC内部累积了静电,但在静电累计过程中IC并未被损伤。此带有静电的IC在处理过程中,当其pin去触碰接地面时,IC内部的静电便会经由pin自IC内部流出来,而造成了放电现象。

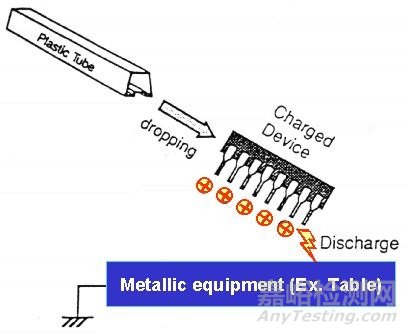

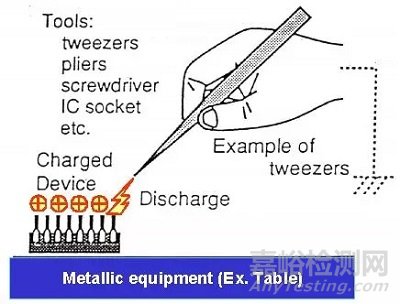

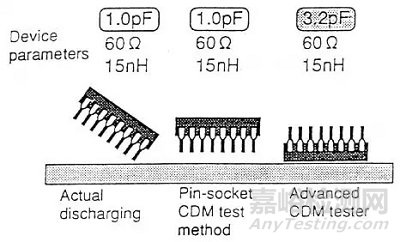

此种模式的放电时间更短,仅约几纳秒以内,而且放电现象更难以被真实模拟。因为IC内部积累的静电会因IC元件本身对地等效电容而变,IC摆放的角度和位置以及IC所用的包装形式都会造成不同的等效电容。由于具有多项变化因素难以确定,因此,有关此模式放电的工业测试标准仍在讨论中,但已有此类测试设备在销售。该元件充电模式(CDM)ESD可能发生的原因以及放电的情形由图5.a和图5.b所示。该元件充电模式静电放电的等效电路图由图6.a所示,IC在各种角度摆放下的等效电容值由图6.b所示,此电容值会导致不同的静电电量累积与IC内部。

图5.aCharged-Device Mode静电放电可能发生的情形。

IC自IC管中滑出后,带电的IC脚接触到地面而形成放电现象。

图5.bCharge-Device Mode静电放电可能发生的情形。

IC自IC管中滑出后,IC脚朝上,但经由接地的金属工具而放电。

图6.a、Charged-Device Model静电放电的等效电路图

图6.b、IC在各种角度下的等效杂散电容值

有关2KV HBM,200V MM,与1KV CDM的放电电流比较,如下图7所示。其中,该1KV CDM的放电电流在不到1ns的时间内,便已经冲到月15安培的尖峰值,但其放电的总时间段约在10ns的时间内便已经结束。此种放电现象更易造成积体电路的损伤。

图7、人体放电模式(2KV),机器放电模式(200V),与元件充电模式(1KV)放电电流的比较图。

1.4、电场感应模式(Field-Induced Model,FIM)

此FIM模式的静电放电发生是因电场感应而起的。当IC因输送带或其他因素而经过一电场时,其相对极性的电荷可能会由一些IC引脚而泄放掉,等IC通过电场后,IC本身便积累了静电荷,此静电荷会以类似CDM的模式放电出来。有关FIM的放电模式早在变栽子(bipolar)电晶体时代就已被发现,现今已有测试标准。在国际电子工业标准(EIA/JEDECSTANDARD)中,也已对此电场感应模式制定测试规范(JESD22-C101),详情请参阅该工业标准。

2、静电放电标准

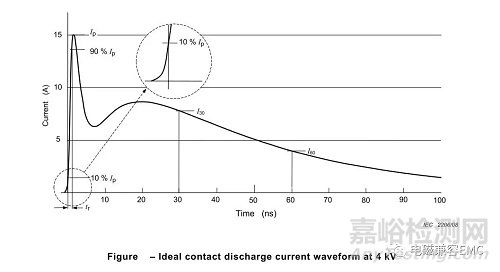

2.1、IEC-61000-4-2or EN-61000-4-2 p.19

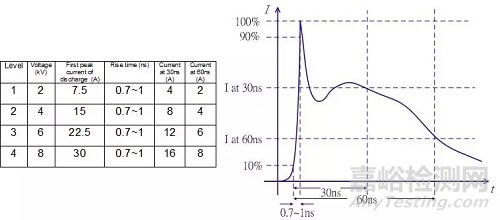

图8、标准规定的静电波形

从这张图可以看出,EMC法规是以电流波形来定义静电枪的输出。又输出能量分两段,第一段的上升时间很短(0.7~1ns),但电流峰值极高(3.75A/KV),此段反映的是HBM(Human Body Mode)放电时,手臂累积的静电荷瞬间放电的结果;第二段(10~60ns)则反映身体累积电荷的释放结果。

注意要点:

(1). 第一根

(2). 第二波放电的高点出现在30ns前

(3). 60ns处的电流值为30ns处电流值的1/2

2.2、ESD GunModel

2.2.1、法规提供的基本模型(EN-61000-4-2p.11)

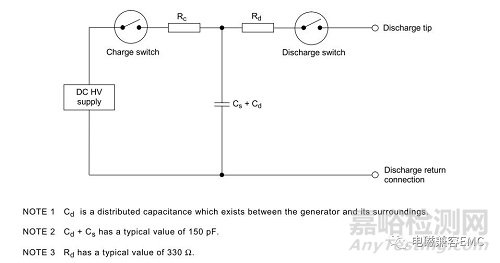

图9、静电枪基本模型

从这张图可以看出,静电枪(ESD Gun/generator)模型除了由RLC lump所组成,还需要两个时序错开的开关,实现充电与放电控制。

这开关在实际电路中采用继电器(relay),而这个继电器有额外引入RLC寄生效应。

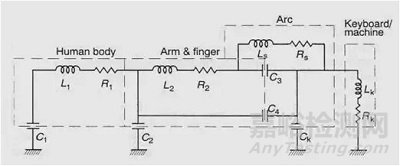

2.2.2、国外教科书的(放电)模型

图10、国外教科书中的放电模型

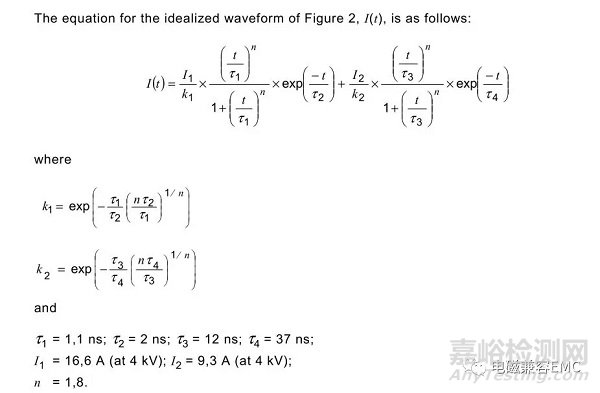

2.2.3、法规定义放电电流数学方程式(EN-61000-4-2 , P13)

图11、EN规定的放电电流方程

3、静电放电模型

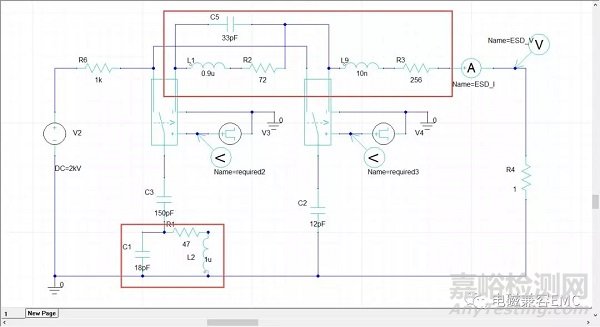

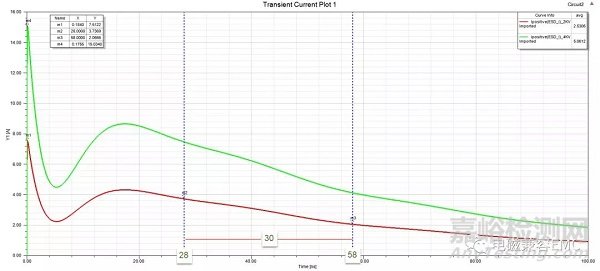

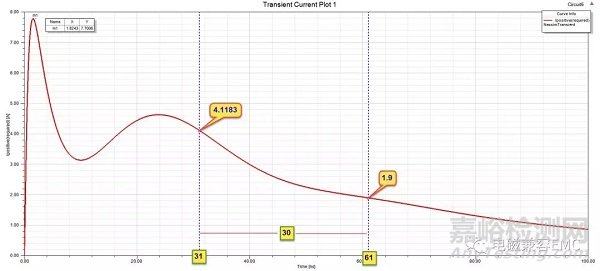

3.1、以两级RLC模拟身体(135~150pF)与手臂(12~15pF)的两波放电模型,输出端以V_Probe与I_Probe观察

图12、模拟电路拓扑及放电电流波形

验证此结果是否满足法规所定义的放电电流波形

2KV:,I=4A at 30ns满足,第一电流点高点出现在0.18ns,且第二波的电流点高点出现在30ns前

4KV:,I=8A at 30ns满足,且第二波的电流高点出现在30ns前

(C2,R3)直接影响第一根的大小,(L1,R2)直接影响第二段(18ns)的波峰大小与出现的时间前后。而充电电容C3对地路径的寄生RLC,则影响第一电流峰值与第二电流峰值间的凹陷特性,这部分对ESD Gun的影响很关键。

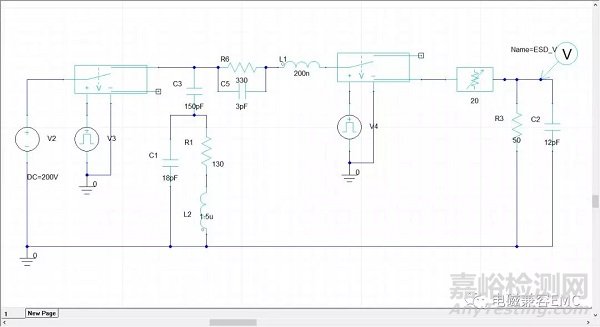

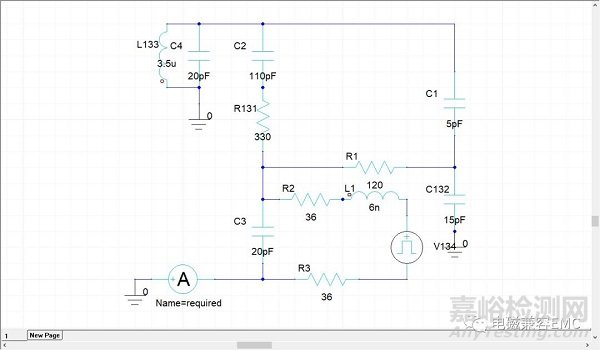

3.2、从法规所提供的基本模型加上静电枪对地寄生RLC的放电模型

3.2.1、在200V放电模式下查看放电电压波形

图13、200V放电电压下的电压波形

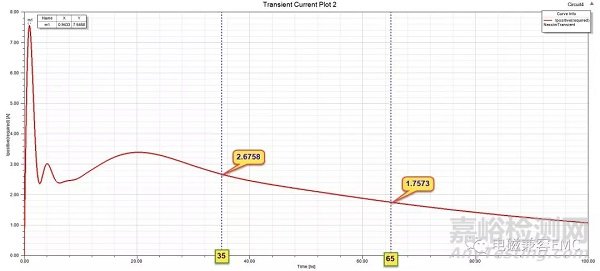

3.2.2、在2KV放电模式下的放电电流波形

图14、2KV放电电压下的电流波形

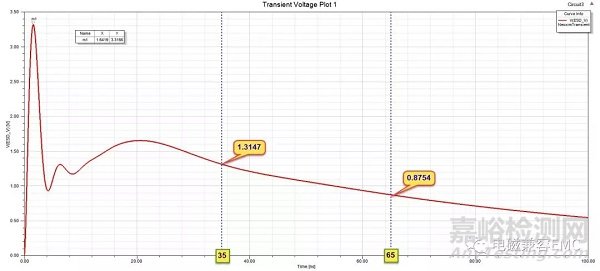

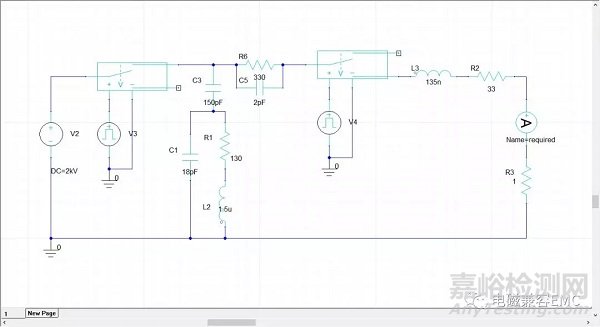

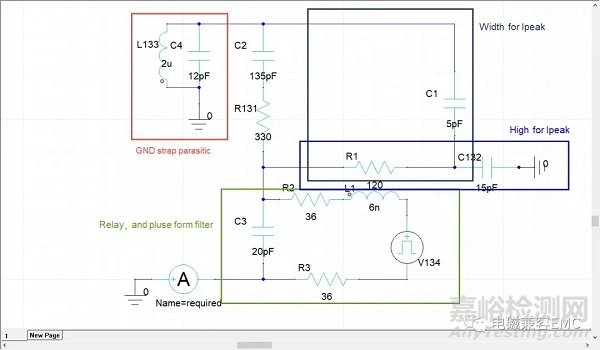

3.3、根据paper【4】【8】所建的ESD Gun等效模型

这个模型虽然是IEEE Trans.的paper,但实际模拟结果却发现其电流输出波形与法规所定义的略有差异:

a. 第一段电流高点出现时间较慢1.82ns(大于0.7~1ns),且图片(大于7.5A)

b. 第二段电流高点出现时间较慢(30ns之后),且 图片on 30+1ns (小于4A)

图15、根据paper【4】【8】所建的ESD Gun等效模型及放电电流

将静电枪对地的(L133,C4)从(3.5uH,20pF)改成(2uH,12pF),以及把充点电容C2从110pF改成135pF,波形就较理想了。

在paper【4】中有提到,实际ESD Gun内的充电电容150pF,但模拟/测量重建用的值却是110pF,为的是让电流衰减速度匹配测量值。

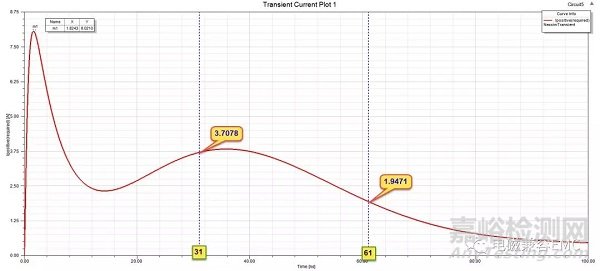

图16、优化后的ESD Gun及其放电电流波形

4. 采用ESD GunModel进行产品EMC设计

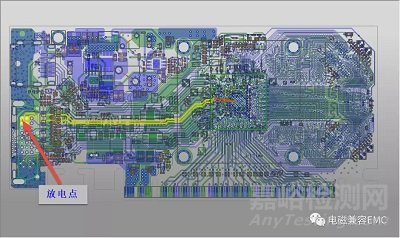

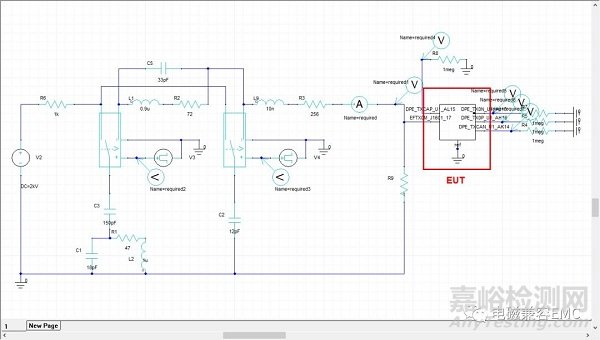

原文采用RLC lump boundary搭建放电枪模型,在HFSS内模拟产品在外加ESD波形下的情况。实际中将PCB和产品外壳放置于HFSS中进行仿真,效率会很低。笔者利用SIwave内含有的HFSS高频求解器,结合circuit designer仿真PCB在外加ESD Gun Model下的端口电压及近场分布情况。

4.1、采用Siwave快速设计PCB静电参数

下面对一块PCB进行仿真,这是一块显卡,视频接口会在使用中外接视频线,因此有ESD风险。我们对其中的一根线进行仿真,采用的ESD Gun Model为3.1节中的放电模型,我们希望分析其在不做任何ESD处理状态下的芯片管脚电压波形(由于没有IC内部芯片模型,我们只分析静电是否会导致信号电平无法识别,而不去分析IC内部是否会由于静电原因烧毁)。因为静电过程中不仅会影响放电pin所在trace的电压,也会影响相邻pin的电压,所以我们选取相邻的几个pin一同分析。

图17、PCB模型及ESD仿真拓扑

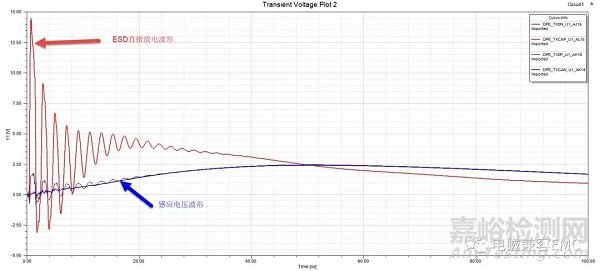

下图为分析结果,可以看到在不加静电处理措施下的PCB,其芯片管脚的电压在ESD冲击下可以达到14.5V之高,而且在初次放电结束后会有众多的振荡产生,这些噪声信号都将使信号电平被淹没其中而不被识别。相邻的信号管脚感应到2.5V的共模噪声,并不会影响到差分电平的识别。对于分析结果,我们会选择相应的措施进行优化,比如常见的加TVS,静电电容等等,关于具体优化措施及其深入讨论后续有时间会另行总结。

图18、分析得到的IC管脚电压波形和近场电场分布

4.2、ESD的频率分布

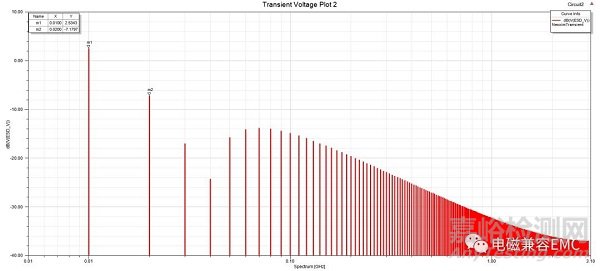

经过前面几节的分析,相信读者已经对ESD的时域波形印象深刻了,但EMC措施的使用往往是基于频域的,ESD的频域特征如何呢,我们用傅里叶变换对标准电压波形进行处理,得到下面结果。

图19、2KV静电放电下的电压频率分布

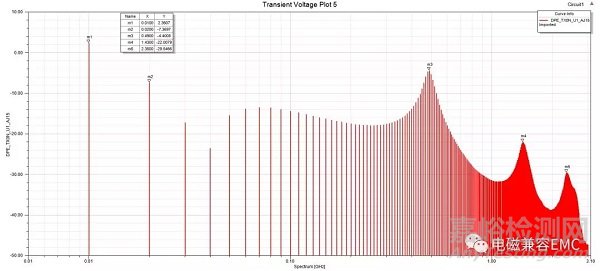

标准ESD放电波形在实际测试中,由于产品内不同分布参数的影响会产生变化,如图18中结果一样,那么实际ESD放电中的频率分布特性是什么样的?我们对图18进行傅里叶变换得到下面结果,对比发现,前面能量最多的10MHz和20MHz没有变化,490MHz和更高频的1.43GHz,2.35GHz出现明显的包络。因此来讲,实际ESD放电可以产生频率丰富的谐波,也正因如此,采用电容等无源器件去处理这些高频谐波来达到抑制ESD变成可能。

图20、实际ESD放电在产品内部的频谱分布

4.3、采用CST进行ESD分析

CST的时域算法为EMC分析提供了便利,下面采用CST进行PCB的全三维ESD仿真,为了准确性,我们可以将产品外壳结构等一同倒入软件,本文不做深入讨论,有兴趣的读者可以自行研究☺。

Reference

【1】台湾交通大学-互补式金氧半积体电路之静电放电防护

【2】网际星空-ESD GunModel and ESD Simulation

【3】IEC-61000-4-2 orEN-61000-4-2

【4】K.Wang, D.Pommerenke,"Numerical Modeling of Electrostatic DischargeGenerators", IEEE Trans, Electromagn. Compat., 2003.

【5】S. Caniggia, F.Maradei, "Circuital and Numerical Modeling of Electrostatic DischargeGenerators", 2005

【6】F. Centola, S. Caniggia, "ESD Extraction Model forSusceptibility Study", 2003

【7】邱冠銘,"Simulation and Measurement of ESD Test for Electronic Devices", 中山大学硕士论文, 2004

【8】 O. Fujiwara, R.Matsuda, "FDTD modeling of ESD Gun", 2005

【9】J.koo, Q.cai,"Frequency-domain measurement method for the analysis of ESD generatorsand coupling", IEEE Trans. on Electromagn. Compat., 2007.

【10】 F. zur Nieden,D. Pommerenke,"A Combined Impedance Measurement Method for ESD GeneratorModeling", EMC Europe, 2011.

【11】 D. C. Smith,Ed Nakauchi, "ESD Immunity in System Designs, System Field experience, andeffects of PWB layout", EOS/ESD Symposium Proceeding, 2000.

【12】 K. H. Kim, Y.Kim,"Systematic Analysis Methodology for Mobile Phone's ElectrostaticDischarge Soft Failures", IEEE Trans. on Electromagnetic Compatibility,2011.

【13】 System LevelESD Part I : Common Misconceptions and Recommended -- 2010

System Level ESD Part II : Implementationof Effective ESD Robust Designs – 2012

【14】 Characterization,modeling, and design of ESD protection circuits (book)

【15】 Jing Li, JunFan, "The Application of Spark gaps on Audio Jack for ESDProtection", IEEE EMC Society, 2013.

【16】 R. Myoung, "Chip-Package-SystemESD Simulation Methodology with Chip ESD Compact Model", DesignCon2014

【17】 Greg Senko,"ESD Simulator Verification", p.34,48, EMC Society 2010

【18】 Janusz Baranand Jan Sroka, "Distortion of ESD Generator Pulse Due to Limited Bandwidthof Verification Path", IEEE Trans. Electromagn. Compat.,2010

来源:电磁兼容EMC