您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2024-07-24 08:30

问题现象描述:

PC模块在进行静电放电测试时,发现对双层USB端子、RJ45端子的金属外壳进行±6KV接触放电测试时出现显示黑屏、画异,拔插HDMI信号后无法正常显示,系统出现宕机、死机现象。

对耳机端子进行±15KV空气放电测试时,也会出现显示黑屏、画异,拔插HDMI信号后无法正常显示,系统出现宕机、死机现象。更换不同的测试样品,测试结果相同,排除个案问题;更换不同的测试场地测试结果相同,排除测试场地的影响。

图1:PC模块实物图

问题现象分析:

根据出现的黑屏、画异后系统宕机、死机现象判断是系统奔溃导致,而对于PC产品来说引起系统奔溃的原因如下:

1、CPU受到静电放电干扰,导致其工作状态异常,系统奔溃后出现宕机、死机现象。

2、DDR模块电路受到静电放电干扰,导致与CPU之间数据交换错误,引发系统奔溃后出现宕机、死机现象。

3、静电放电干扰引发系统供电电源电压波动,波动范围超过系统供电电压容限范围时,系统工作异常出现宕机、死机现象。

4、系统存储模块如SATA硬盘、固态硬盘等模块受到静电放电干扰,出现数据交换错误,从而导致系统奔溃,宕机。

图2:端子金属外壳贴导电布于屏蔽盒体上

该产品的设计工程师反馈已经尝试过的如下改善试验:

1、将RJ45端子的金属外壳用导电胶布贴附于屏蔽盒上,将静电放电干扰直接泄放到金属屏蔽盒体上,降低流过板卡上的静电电流,减小对板卡上敏感信号的冲击。

2、将双层USB端子的金属外壳用导电胶布贴附于屏蔽盒上,将静电放电干扰直接泄放到金属屏蔽盒体上,降低流过板卡上的静电电流,减小对板卡上敏感信号的冲击。

3、将HDMI端子的金属外壳用导电胶布贴附于屏蔽盒上,将静电放电干扰直接泄放到金属屏蔽盒体上,降低流过板卡上的静电电流,减小对板卡上敏感信号的冲击。

4、HDMI端子接地引脚底层增加焊锡,加大接触面后使用导电泡棉到金属屏蔽盒,企图使流入板卡的静电电流再次分流到屏蔽金属盒。

5、双层USB端子接地引脚底层增加焊锡,加大接触面后使用导电泡棉到金属屏蔽盒,企图使流入板卡的静电电流再次分流到屏蔽金属盒。

6、RJ45端子接地引脚底层增加焊锡,加大接触面后使用导电泡棉到金属屏蔽盒,企图使流入板卡的静电电流再次分流到屏蔽金属盒。

尝试对策验证结果:静电放电测试结果,改善效果不明显,证明对策无效。

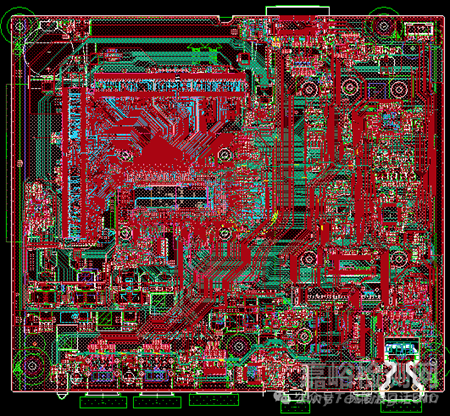

图3:产品PCB Layout图

根据产品电子工程师提供的排查试验,基本排除板卡接地状态的影响,根据问题现象进行USB、RJ45、HDMI、耳机端子 PCB Layout的排查:

1、查阅PCB Layout 图,未发现有CPU、DDR芯片的控制信号、供电电源布线靠近USB端子附近,不存在敏感信号靠近USB端子被静电放电干扰的可能性。

2、查阅PCB Layout 图,未发现有CPU、DDR芯片的控制信号、供电电源布线靠近RJ45端子附近,不存在敏感信号靠近USB端子被静电放电干扰的可能性。

3、查阅PCB Layout 图,未发现有CPU、DDR芯片的控制信号、供电电源布线靠近HDMI端子附近,不存在敏感信号靠近USB端子被静电放电干扰的可能性。

4、拆机分析过程中,注意到DDR模块靠近金属外壳非常近,初步怀疑可能是DDR电路模块受到金属屏蔽壳体上静电放电噪声干扰,与电子工程师沟通确认到如下信息:

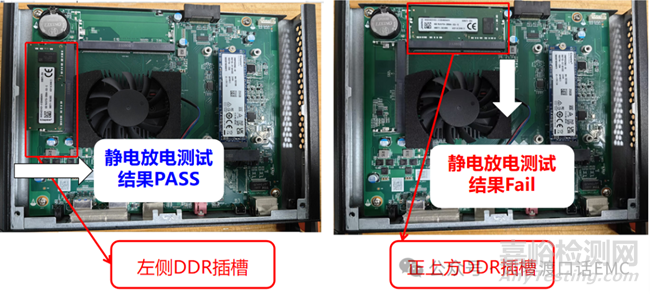

5、此PC模块支持双DDR插槽,可以同时使用双DDR模块,当单独使用左侧DDR插槽的时候,静电放电测试结果是符合标准要求的,结论判定PASS。

6、当单独使用正上方DDR插槽的时候,静电放电测试结果是不符合标准要求的,结论判定Fail;同时使用两颗DDR插槽的时候,静电放电测试结果是不符合标准要求的,结论判定Fail。

图4:更换DDR插槽试验图示

问题根因分析:

不同DDR插槽使用相同DDR颗粒静电放电测试结果差异巨大,分析判断问题产生的原因有如下可能性:

1、左侧DDR插槽在插入DDR颗粒后,DDR颗粒距离金属屏蔽壳体比正上方DDR插槽在插入DDR颗粒后距离金属屏蔽壳体的距离大很多,静电放电时屏蔽金属壳体对DDR颗粒的干扰要小。

2、左侧DDR插槽PCB Layout布线信号参考的完整性相比于正上方DDR插槽PCB Layout布线信号参考的完整性要更优,对静电放电干扰免疫力更强。

不同DDR插槽PCB Layout对比分析情况如下:

1、左侧DDR插槽信号布线在1、3层,其中顶层信号参考第2层完整的地平面,3层信号布线参考底层完整的地平面。

2、正上方DDR插槽信号布线在1、3层,其中顶层与第3层的数据信号、DQS、关键控制信号布线分别参考第2层和底层完整的地平面;顶层与第3层的地址信号布线参考第2层和底层完整的DDR供电电源平面。

3、地址信号线参考DDR本身的供电电源平面有过很多成功案例,暂且不怀疑地址信号线与数据信号线参考不同平面的影响。

在正上方DDR插槽中分别使用不同品牌DDR颗粒,进行静电放电测试验证,结果如下:

1、正上方DDR插槽使用金士顿内存条,进行静电放电测试时,测试结果不符合内部管控标准要求,判定结果Fail。

2、正上方DDR插槽使用合肥长鑫内存条,进行静电放电测试时,测试结果符合内部的管控标准要求,判定结果PASS。

3、使用合肥长鑫DDR内存条验证两台机器,反复测试多次结果均符合内部管控标准要求,判定结果PASS。

图5:不同品牌内存颗粒静电放电测试结果对比

问题根因分析:

静电放电干扰对DDR颗粒耦合路径分析如下:

1、对金属端子的外壳进行进行静电放电测试时,由于金属端子外壳与屏蔽金属壳体直接连接,或者静电放电直接耦合到金属屏蔽壳体上,由于金属壳体本身未接地,金属壳体则很容易积累电荷,存在电场干扰。

2、由于结构设计、PCB Layout布局设计原因,正上方DDR插槽插上DDR颗粒后使得DDR颗粒本体靠近金属屏蔽壳体,金属壳体上的静电放电干扰通过空间耦合到DDR颗粒上面,加之DDR颗粒本身抗静电能力差异,导致DDR颗粒工作异常,数据交换错误,引起系统奔溃,出现黑屏、画异后系统宕机、死机现象。

3、通过观察、分析合肥长鑫与金士顿的内存颗粒PCB Layout图,判断差异来自DDR布线与PCB边缘距离差异导致;具体就是金士顿内存颗粒PCB布线更靠近PCB边缘,而合肥长鑫的内存颗粒PCB Layout布线距离板边较远。

图6:DDR颗粒静电放电干扰耦合路径图解

问题解决方案

问题解决方案(一):

修改PCB Layout设计,将正上方DDR插槽内移,使其远离金属屏蔽壳体,降低两者之间的空间耦合。

问题解决方案(二):

使用单颗DDR内存时,优先使用左侧DDR插槽,避免使用正上方的DDR插槽,避免DDR颗粒被金属屏蔽壳体上的静电噪声干扰。

问题解决方案(三):

当使用两颗DDR内存时,优先使用合肥长鑫生产制造的DDR颗粒,增强DDR颗粒本身的抗静电放电干扰的能力。

【案例总结】:

PCB Layout设计过程中,在PCB布局评审时应重点关注DDR模块电路等敏感信号、电路、元件远离PCB板边缘,或者远离静电放电测试点,避免静电放电测试或者其它抗骚度时干扰敏感信号。

对于内存条这类敏感器件更换时不仅仅需要测试辐射发射,还需要进行抗骚度性能的测试,同时需要关注应用场景的影响。

不同厂商、不同品牌的关键器件导入时,需要进行相关的EMC性能测试,并做好充分的性能评估,否则可能导致严重的EMI问题或严重的抗骚度问题。

来源:风陵渡口话EMC