您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2024-10-18 12:49

《半导体器件的失效机理和模型》将针对硅基半导体器件常见的失效机理展开研究。这些失效机理大致按照从硅到封装器件的半导体生产工艺流程进行了分类:前段制程(FEoL)、后段制程(BEoL)和封装/界面失效机理。

注:失效机理研究只包括那些业界相对成熟,同时还包括这些失效机理的模型研究现状。内容主要来源为国内外文献的翻译整理,供大家学习参考。

各阶段常见的典型失效机理

前段制程(FEoL)常见的失效机理

1)与时间相关的电介质击穿(TDDB)-- 栅极氧化物

2)热载流子注入(HCI)

3)负偏压温度不稳定性(NBTI)

4)表面反转(移动离子)

5)浮栅非易失性存储器数据保持

6)局部电荷捕获非易失性存储器数据保持

7)相变(PCM)非易失性存储器数据保持

后段制程(BEoL)常见的失效机理

1)与时间相关的电介质击穿(TDDB)-- 层间电介质/低k值/移动铜离子

2)铝电迁移(Al EM)

3)铜电迁移(Cu EM)

4)铝和铜腐蚀

5)铝应力迁移(Al SM)

6)铜应力迁移(Cu SM)

封装/界面常见的失效机理

1)因温度循环和热冲击导致的疲劳失效

2)因温度循环和热冲击导致的界面失效

3)因高温导致的金属间化合物和氧化失效

4)锡须

5)离子迁移动力学(PCB)--组件清洁度

本文对FEoL阶段的非易失性存储器数据保持模型进行研究

浮栅非易失性存储器是一种非易失性的存储器,即器件断电后数据也不会丢失。它基于浮栅晶体管,通过其中所存储的电荷量表示不同的数据。常见的U盘、存储卡、固态盘(SSD)等设备的存储介质就是浮栅非易失性存储器。浮栅晶体管典型结构如下图所示。

1)控制栅:用于控制晶体管的工作状态,通过给控制栅极施加不同的电压,可以实现对浮栅层中电荷的充放,来控制晶体管的导电性。

2)氧化层:位于控制栅和浮栅层之间,以及浮栅层和隧道氧化层之间,起到绝缘的作用,使得电荷在浮栅层中可以保持较长时间而不泄漏。

3)浮栅层:被绝缘氧化层包裹,形成一个电荷存储的“浮岛”,电荷注入到浮栅层后会被困在里面,只有特定的操作才能移除。该特性使浮栅晶体管可以非易失性地存储信息。

4)隧道氧化层:位于浮栅和衬底之间的一层薄氧化层,电子在某些操作下可以通过隧道效应穿过该氧化层进入或离开浮栅层。

当浮栅充电时,它被识别为“编程”状态并标记为0;当浮栅没有电荷时,它被识别为“擦除”状态并标记为1。浮栅内部捕获的电子数量与单元晶体管的阈值电压成正比。若捕获大量电子,晶体管则实现高阈值电压;若捕获少量电子,则形成低阈值电压。如果周围的电路没有改变,浮栅处于绝缘状态,其存储的电荷就保持状态不变。

非易失性存储器会受到多种可能导致数据丢失的机制的影响。对于浮栅存储器,一个单元的数据(“0”或“1”)取决于其阈值电压(VT)是高于还是低于临界阈值水平(VT,Crit)。VT可能会随时间漂移,从而导致单元数据发生变化。阈值漂移最常见的退化模型是电介质电荷泄漏和电介质中的电荷从陷阱中释放。这两个模型适用于7~12nm厚的隧道氧化层的浮栅存储器。

浮栅非易失性存储器数据保留模型

有几种微观机制导致了浮栅非易失性存储器的数据退化模型,这些机制中的大多数都与单元隧道氧化物中存在缺陷有关。在多次的数据编程/擦除(P/E)循环过程中会导致隧道氧化物的退化并产生缺陷,使电荷可以从浮栅和隧道氧化物中跑出来致使VT不稳定。

导致阈值电压不稳定的主要因素的模型:

1)SILC(Stress-Induced Leakage Current,简称 SILC):陷阱辅助隧穿(trap-assisted tunneling,简称TAT)导致浮栅电荷泄漏;

2)界面态退火:通过增强沟道电导率影响单元阈值电压;

3)电荷去捕获:源于电荷在氧化物缺陷中的捕获及其中和。

在2X-nm和1X-nm NAND Flash节点进行的研究表明,这些模型可以同时起作用,并且它们对整体VT偏移(ΔVT)的相对权重不仅取决于器件的工作条件,还取决于器件采用的技术。

特别需要注意的是,失效模型的影响不能简单地叠加,因为这些模型并非相互独立。例如,当闪存单元处于擦除状态(负VT)时,此时隧道氧化物场将去陷阱电子推向浮栅层。在这种情况下,在低循环次数时陷阱辅助隧穿占主导地位;在高循环次数时大量的去陷阱电荷向浮栅层聚集,导致浮栅势垒能量提高,陷阱辅助隧穿发生的可能性降低。

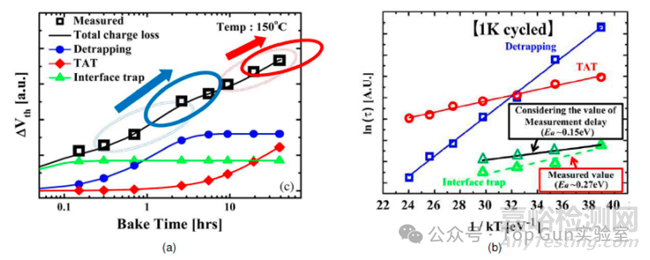

(a)影响 ΔVT 的失效模型退化曲线,(b)每种模型的 Eaa 提取

为了准确建模和预测闪存阵列的可靠性,不仅需要了解各种失效模型对VT的影响,还需要评估它们与温度的相关性。通过设计加速寿命测试,有效预测设备的正常使用条件下的表现。通常,利用阿列纽斯模型可以获得上述三个模型的温度相关性,并提取每种模型的热活化能(Eaa)。

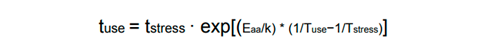

电荷去捕获的Eaa约为1.1eV,陷阱辅助隧穿和界面态退火的热活化能较弱,Eaa值分别为0~0.3eV和约为0.15eV。因此,和温度相关的加速寿命公式如下:

模型研究

1)由编程/擦除循环引起的与SILC相关的介电泄漏模型

应力诱导泄漏电流(Stress-Induced Leakage Current,简称 SILC)。SILC归因于陷阱辅助隧穿,即电子或空穴通过应力产生的陷阱从一个电极隧穿到另一个电极。在存储器中,编程/擦除循环会导致陷阱的产生,由此产生的SILC会导致VT漂移。VT漂移会导致已编程的闪存单元会失去电子(电荷损失),或已擦除的闪存单元获得电子(电荷增益)。故障时间取决于循环次数、温度、施加电压以及临界阈值水平(VT,Crit):

在SILC加速模型中,通常忽略温度加速,因为热活化能(Eaa)较低,而且高温会导致氧化物恢复;一般使用电场加速,施加VG监控是否触发(VT,Crit)。

注:上述模型公式已被证明能准确拟合某些器件采用的技术试验结果。但对于部分器件采用的技术,有报告称其与循环次数的纯幂律依赖关系以及与电压的纯指数依赖关系存在偏差。此外,在某些器件中观察到,当达到某个阈值电压时,阈值漂移会突然停止。上述模型未涵盖这些效应。

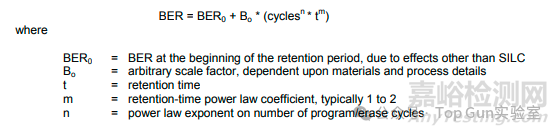

对于给定的 VT,Crit和VG,处于错误状态的比特比例,称为比特错误率(bit error rate,简称BER):

注:在设计有纠错码(ECC)的闪存中,与SILC相关的泄漏电荷可能会导致一些存储位即使在未加速条件下也会失效,由于BER未达到超过ECC能力的阈值,所以不会发生数据丢失。在这种情况下,可以使用另一种方法:可以将BER作为时间的函数进行测量,拟合到方程,外推到超出应力时间的时间,然后与ECC能力进行比较。

2)电荷去捕获模型

当陷阱位于沟道上方时,所产生的陷阱会直接影响器件的VT,且如果陷阱中载流子在偏置条件或高温条件下脱陷,VT将会偏移。

表征电荷去捕获影响因素:

1)编程/擦除循环:对存储单元进行编程/擦除的操作;

2)数据保留烘烤:是指在高温下不加偏置进行烘烤,以加速存储节点处电荷的损耗。

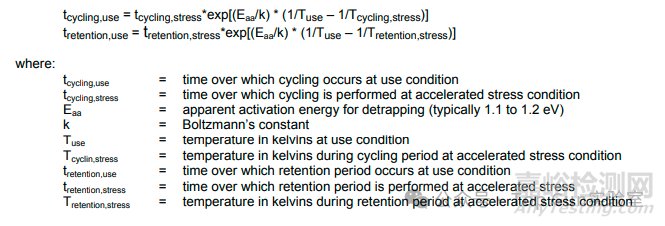

电荷去捕获导致的VT偏移不仅仅和时间-温度相关,还与编程/擦除的时间-温度相关,因为在编程/擦除循环之间的延迟会发生显著的脱陷。因此,加速寿命模型并不只有一个等效公式,而是两个这样的等效公式,一个用于编程/擦除循环,一个用于数据保持:

数据保留寿命预估示例:

目标:

针对电荷去捕获和SILC模型,计算正常使用环境与加速环境下数据保留失效的加速因子(AF)。对于电荷去捕获,考虑编程/擦除循环次数的影响。对于SILC,使用电压加速方法计算加速因子。另外,对于SILC,使用外推误码率方法计算失效的保留时间。

假设条件:

1)正常使用条件为:50°C芯片温度和在2年的时间里进行100,000次编程/擦除循环,随后是数据保持。

2)SILC加速条件为:在进行了100,000次编程/擦除循环后,随后在25°C的数据保持。

对于电压加速法,VT,Crit裕量预留2V。

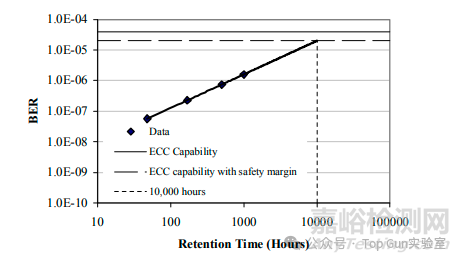

对于BER推断法,假定ECC方案的BER能力为4x10-5,对未经加速的1000小时数据保持结构进行测试,测量点为48、168、500和1000小时。

3)电荷去捕获加速条件为:在85°C下进行100,000次编程/擦除循环,随后在125°C下数据保持。

AF计算公式:

BER的数据点外推:数据符合纯幂律关系,ECC的能力为4x10-5,除以2以确保安全裕度(如水平虚线所示)。外推的BER线与该水平虚线相交于10,000小时,这是估计的数据保留时间。

结论:

1)对于电荷去捕获,选择85°C下100,000次编程/擦除循环,然后选择125°C进行数据保持,经计算加速因子为1711倍。

2)对于SILC,VT,Crit裕量=2V,加速因子为99倍。

3)对于用BER-acceleration方法评估的SILC数据保持,数据外推TTF为10,000小时。

参考文献:

1)Mielke, N., et al., “Flash EEPROM Threshold Instabilities due to Charge Trapping During Program Erase Cycling,” IEEE Transactions on Device and Materials Reliability, Vol. 4, Issue 3, 2004, pp. 335-344.

2)Mielke, N., et al., “Recovery Effect in the Distributed Cycling of Flash Memories,” IEEE International Reliability Physics Symposium Proceedings, 2006, pp. 29-35.

3)C. Compagnoni, C. Miccoli, R. Mottadelli, S. Beltrami, M. Ghidotti, A. L. Lacaita, A. S. Spinelli and A. Visconti, “Investigation of the threshold voltage instability after distributed cycling in nanoscale NAND Flash memory arrays” IEEE International Reliability Physics Symposium Proceedings, 2010.

4)Mielke, N.R., “New EPROM Data Loss Mechanisms,” IEEE International Reliability Physics Symposium Proceedings, 1983, pp. 106-113.

5)J.-D. Lee, J.-H. Choi, D. Park, and K. Kim, “Effects of interface trap generation and annihilation on the data retention characteristics of Flash memory cells,” IEEE Trans. Device Mater. Rel., vol. 4, pp. 110–117, Mar. 2004.

6)R. Yamada, Y. Mori, Y. Okuyama, J. Yugami, T. Nishimoto, and H. Kume, “Analysis of detrap current due to oxide traps to improve flash memory retention,” in Proc. IRPS, pp. 200–204, 2000.

7)K. Lee, M. Kang, S. Seo, D. H. Li, J. Kim, and H. Shin, “Analysis of failure mechanisms and extraction of activation energies (Ea) in 21-nm NAND Flash cells,” IEEE Electron Device Lett., vol. 34, pp. 48–50, Jan. 2013.

8)K. Lee, M. Kang, S. Seo, D. Kang, S. Kim, D. H. Li, and H. Shin, “Activation energies (Ea) of failure mechanisms in advanced NAND Flash cells for different generations and cycling,” IEEE Trans. Electron Devices, vol. 60, pp. 1099–1107, Mar. 2013.

9)K. Lee, D. Kang, H. Shin, S. Kwon, S. Kim, and Y. Hwang, “Analysis of failure mechanisms in erased state of sub 20-nm nand flash memory,” in Proc. ESSDERC, pp. 58–61, Sept. 2014.

10)C. Miccoli, C. Monzio Compagnoni, S. Beltrami, A. S. Spinelli, and A. Visconti, “Thresholdvoltage instability due to damage recovery in nanoscale NAND Flash memories,” IEEE Trans. Electron Devices, vol. 58, pp. 2406–2414, Aug. 2011.

来源:Top Gun实验室