您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2024-11-01 12:03

项目场景:

二级BUCK电源电路,DCDC芯片输入5V,输出0.74V,开关频率2.1MHz。工作在FCCM模式。

如下图1所示:

问题描述

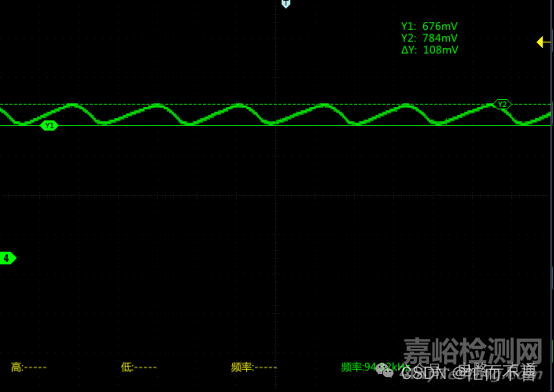

1、测试发现输出电压纹波超过100mV,纹波频率约94kHz。不满足后级芯片对纹波噪声的要求。如下图

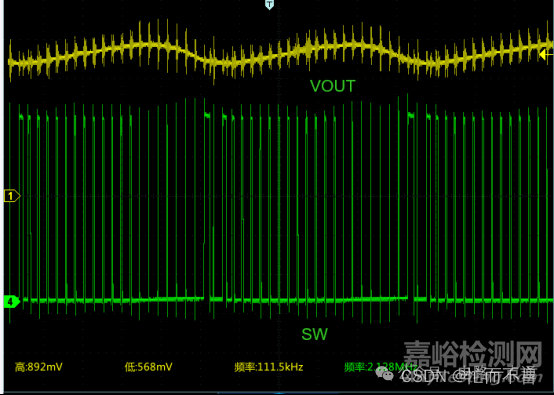

2、如下图,同时测量SW管脚信号和输出信号。其中绿色是DCDC的SW管脚信号,黄色是输出电压(上面的毛刺脉冲是探头串扰,实际波形见上图1) 。可以看出SW信号的脉冲宽度是一直在变化的,从而也导致输出电压不断变化,变化趋势与SW的变化对应。

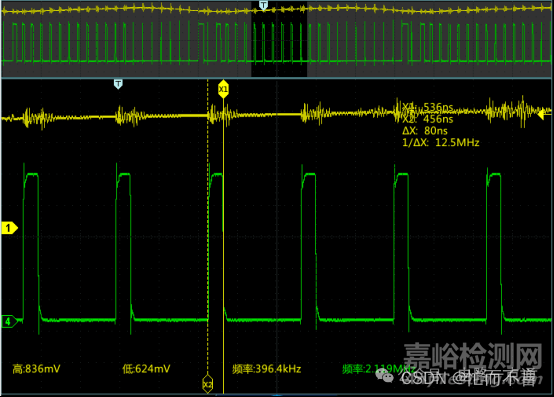

如下图3,输出电压最低点开始,脉冲宽度持续10来个周期一直在80ns左右

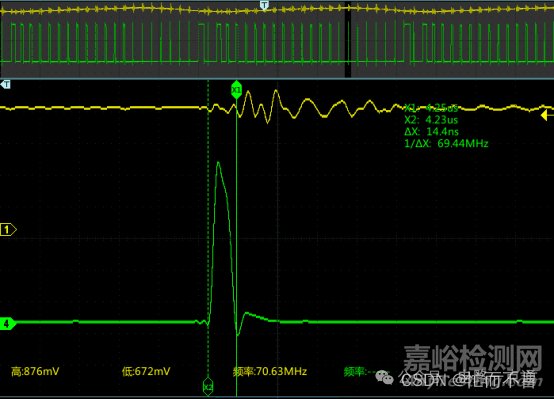

3、输出电压达到最高点后,输出脉冲宽度变成14ns左右的尖峰脉冲。然后导致输出电压开始下降。

原因分析:

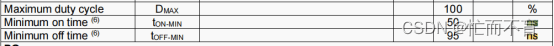

SW脉冲宽度变化的原因与DCDC的最小导通时间有关。理论计算SW信号的高电平脉冲宽度约等于0.74V/(5V*2.1MHz)=69ns。DCDC手册上要求Minimum on time 时间Typ值为50ns,没有给出Minimum on time的最大最小值。与DCDC芯片厂家确认,这个最大值大概在75ns~80ns。与上面实际测试结果中的80ns相符。

由于实际要求的导通时间是69ns,而DCDC高侧MOS至少要打开80ns(Minimum on time),几个周期后就会把输出冲高,但是FB比较器反馈的结果又需要关闭Switch,从而让输出变低,相当于引入了一个干扰源。从而导致了大的输出波纹。

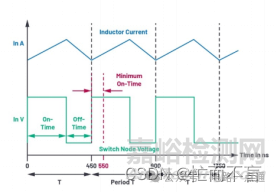

什么是最小导通时间,为什么需要有最小导通时间? 在许多开关模式电源转换器中,电感电流是在导通时间内测量的。此电流用于过流保护,并用于根据电流闭环控制原理(电流模式控制)工作的稳压器中,环路调节也需要测量电感电流。在开关瞬变后,必须先降开关过程中产生的噪音才能进行准确的电流测量。这需要一些时间,也称为消隐时间。而这段时间内内置的电流限制比较器也不会工作,高侧MOS的Gate输出驱动也就不会被关断。

解决方案:

根据上述的分析结论,做了一些验证:

1、提高输出电压,增大高电平占空比---输出电压纹波消失

2、降低输入电压,增大高电平占空比---输出电压纹波消失

3、降低开关频率------输出电压纹波消失

上述验证结果证实了前面的分析结论。但由于输入电压和输出电压都不能改变,所以最终选择降低开关频率。

开关频率由2.1M变成1.38M,SW脉冲宽度理论值为:0.75V/(5V*1.38MHz)=108ns,大于Minimum on time要求的最大值80ns。

总结:DCDC电源电路设计的时候需要考虑电源IC的最小导通时间(Minimum on time或者称为消隐时间),而且要保证实际需要的导通时间大于Minimum on time的最大值,如果芯片中没有体现最大值要求,需要找厂家确认清楚。否则电源输出会有问题。

来源:Internet