摘要:集成电路塑封器件的早期失效一般由设计或工艺失误所致,通过常规电性能检测和筛选可判别这些失效的器件。而使用期失效则是由于器件的潜在缺陷引起,潜在缺陷的行为与时间和应力有关。分析塑封器件常见失效模式及其机理,有助工程师在设计时充分考虑使用环境的特性,提高塑封器件的可靠性。

自1962年开始出现塑封半导体器件,因其在封装尺寸、重量和成本等方面的优势性,用户愈来愈多的采用塑封器件代替原先的金属、陶瓷封装器件。但塑封器件在发展初、中期可靠性水平较低,在80年代之后,随着高纯度、低应力的塑封材料的使用,高质量的芯片钝化、芯片粘接、内涂覆材料、引线键合、加速筛选工艺及自动模制等新工艺技术的发展,使得塑封器件的可靠性逐步赶上金属封装与陶瓷封装的器件。

一般塑封器件的失效可分为早期失效和使用期失效,前者多是由设计或工艺失误造成的质量缺陷所致,可通过常规电性能检测和筛选来判别。后者则是由器件的潜在缺陷引起的,潜在缺陷的行为与时间和应力有关,经验表明,受潮、腐蚀、机械应力、电过应力和静电放电等产生的失效占主导地位。

1 失效模式及其机理分析

塑封器件,就是用塑封料把支撑集成芯片的引线框架、集成芯片和键合引线包封起来,从而为集成芯片提供保护。塑封器件封装材料主要是环氧模塑料。环氧模塑料是以环氧树脂为基体树脂,以酚醛树脂为固化剂,再加上一些填料,如填充剂、阻燃剂、着色剂、偶联剂等微量组分,在热和固化剂的作用下环氧树脂的环氧基开环与酚醛树脂发生化学反应,产生交联固化作用使之成为热固性塑料。塑封材料不同于陶瓷材料和金属材料,它是一种高分子复合材料,其固有的有机大分子结构,使其本身存在较高的吸湿性,是一种非气密性封装。塑封材料主要失效模式为:开路,短路,参数漂移,烧毁。由于塑封器件是非气密性封装,在封装方面就存在一些缺点,最主要的缺点就是对潮气比较敏感。

受潮。塑封材料会从环境中吸收或吸附水气,特别是当塑封器件处于潮湿环境时,会吸收或吸附较多的水气,并且在表面形成一层水膜。受潮是塑封器件的很多失效机理如腐蚀、爆米花效应等的诱因。

腐蚀。对塑封器件而言,湿气渗入是影响其气密性导致失效的重要原因之一。湿气渗入器件主要有两条途径:(1)由于树脂本身的透湿率与吸水性,水气会直接通过塑封料包封层本体扩散到芯片表面;(2)通过塑封料包封层与金属框架间的间隙,然后再沿着内引线与塑封料的封接界面进入器件芯片表面。

当湿气通过这两条途径到达芯片表面时,在表面形成一层导电水膜,并将塑封料中的Na+、CL-离子也随之带入,在电位差的作为下,会加速对芯片表面铝布线的电化学腐蚀,最终导致电路内引线开路。随着电路集成度的不断提高,铝布线越来越细,因此,铝布线腐蚀对器件寿命的影响就越发严重。

其腐蚀机理均可归结为铝与离子沾污物的化学反应:由于水汽的浸入,加速了水解物质(Na+、CL-)从树脂中的离解,同时也加速芯片表面钝化膜磷硅玻璃离解出(PO4)3-。腐蚀过程中离解出的物质由于其物理特性改变,例如脆性增加、接触电阻值增加、热膨胀系数发生变化等,在器件使用或贮存过程中随着温度及加载电压的变化,会表现出电参数漂移、漏电流过大,甚至短路或开路等失效模式,且有些失效模式不稳定,在一定条件下有可能恢复部分器件功能,但是只要发生了腐蚀,对器件的长期可靠性将埋下隐患。

爆米花效应。随着SOP、PLCC、PQFP、BGA等表面安装封装技术的发展,由于塑封体吸湿性引起的开裂问题已越来越突出。塑封体通过扩散吸收水分最终会使封装体与周围环境在一定的温度和湿度条件下达到一种平衡状态。此时,该塑封体放入回流炉内加热回流焊,塑封体内的水分在高温下变成气体,形成饱和水蒸气,随着蒸气量的增加,在封装体内产生蒸气压,当压力达到一定的程度,为释放压力,在应力集中薄弱处就产生裂纹,塑封体从内部开始产生裂纹,引起分层剥离和开裂现象,俗称“爆米花”效应。如图1所示为一过回流焊后表面出现鼓起的芯片。

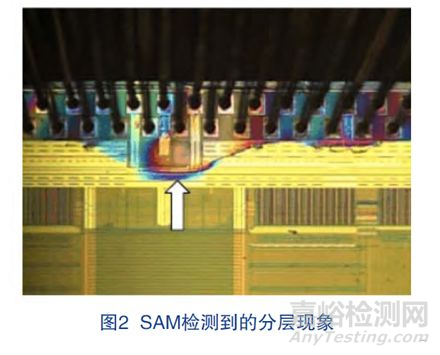

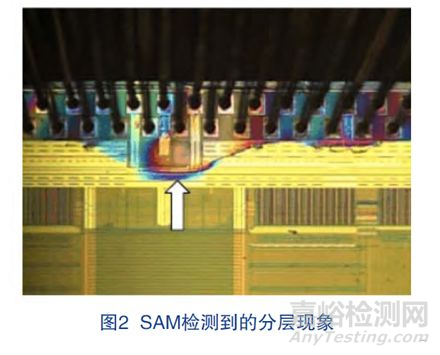

在塑封器件中,塑封层与芯片、塑封层与基板(功率器件的散热器、单片IC 的芯片支架、多心芯片或BGA 封装形式的PCB 板等)之间的界面容易出现分层的现象(图2)。因为塑封层与其他材料之间的界面属于粘合结构,界面的两种材料通过分子之间的作用力结合在一起,而不是两种材料互溶、互扩散、形成化合物的过程。

塑料封装器件塑封层与其他材料之间的界面出现分层现象,可引起器件性能下降、甚至失效。如:分层发生在塑封层与芯片的界面,一方面,可引起芯片的键合引线由于机械拉伸,键合引线(包括内、外键合点)翘起、键合接头开裂和键合引线断开等机械损伤而导致连接电阻增大或开路;另一方面,可引起芯片表面钝化层损伤,导致芯片漏电增加、击穿电压下降、金属化条断裂等;再者,塑封层与芯片界面的分层,会给水分和污染物的侵入提供通道,从而影响长期可靠性。

塑封器件塑封层与其他材料界面一旦发生分层现象,即使分层面积小,但在器件使用过程中,由于热变应力或机械应力的作用,分层不断扩展,随着分层面积的增大,最终导致器件失效。

2 EOS/ESD

过电应力(Electrical Over Stress,EOS)是指元器件承受的电流或电压应力超过其允许的最大范围。EOS来源于对器件引脚施加持续的较大电压或电流应力,时间长短和电流大小决定着对器件施加能量的高低。通常情况下使EOS 发生的电应力要持续1ms以上,但 μs量级的电应力也能造成过电力现象的产生。EOS造成的损伤主要表现为元器件性能严重劣化或功能失效。器件受EOS损伤会在局部形成热点,当局部热点温度达到材料熔点时使材料熔化,形成开路或短路,导致器件烧毁。

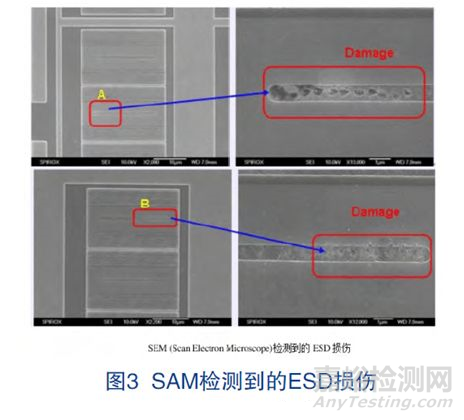

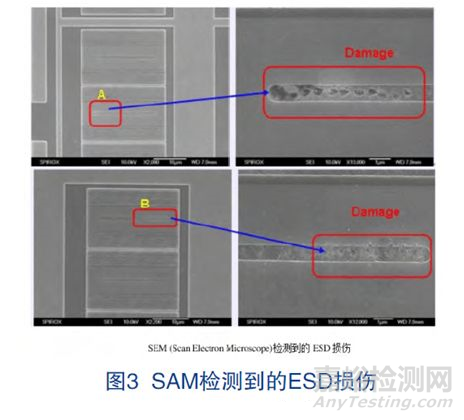

静电放电(Electrostatic Discharge,ESD)是指处于不同静电电位的两个物体间的静电电荷的转移。这种转移的方式有多种,如接触放电、空气放电。静电放电(ESD)引发的失效(图3)可分为突发性失效和潜在性失效两种,突发性失效是指器件受到静电放电损伤后,突然完全丧失其规定的功能,主要表现为开路、短路或参数严重漂移;潜在性失效是指静电放电能量较低,仅在器件内部造成轻微损伤,电参数仍然合格或略微变化,但其抗过电应力能力已明显削弱,这样随着它的继续使用将逐步导致失效。

由ESD导致器件的失效通常情况下被认为是EOS失效的一个分支。因为两者具有相似的电性失效模式和物理失效特征。关键是区分对于导致ESD和EOS失效所施加应力的临界点。对于塑封器件,电路EOS/ESD损伤, 通过导电塑料的电流旁路过热,从而造成芯片上局部高温区塑料碳化的现象。这种失效机理使封装剂退化,使其绝缘电阻受到损耗而导电。大电流沿着这条导电通道并通过塑料从电源输送到地线,不断使塑料发热,最终使塑封器件烧毁。

3 机械应力作用

由于模塑料、芯片、金属框架的线膨胀系数不匹配而产生的内应力,对器件密封性有着不可忽视的影响。因为模塑料膨胀系数(20-26E-6/℃)较芯片、框架(-16E-6/℃)大,在注模成型冷却或在器件使用环境的温差较大时,有可能导致塑封料在芯片上移动。这种应力对芯片表面结构构成一种剪切力,它首先使芯片上附着力弱的金属化层向芯片中心滑移,造成金属化铝条间开路或短路;也可能造成钝化层或多晶硅层破裂,多层金属化上下层间短路。另外,塑封料在工作温度下会对芯片有一个压应力。温度越低,压应力越大。同时塑封料中加了石英砂填料,以其尖锐的角尖接触芯片,塑封料的压力传递到芯片上,刺破钝化层和金属层造成开路或短路,也会造成器件参数变化。

4 生产工艺缺陷

塑封成形缺陷。造成塑封器件失效的原因有许多,许多都是与封装工艺、封装材料等有关。塑料成形缺陷主要有:塑封材料未充填完整、气孔、麻点(表面多孔)、冲丝、小岛移动、开裂、溢料等。塑封料在注塑成形时呈熔融状态,是有黏度的运动流体,因此具有一定的冲力。冲力作用在金丝上,使金丝产生偏移,极端情况下金丝冲断,就是所谓的冲丝。冲丝缺陷涉及到键合和塑封两个工序,产生的原因有很多,如塑料黏度过大、金丝过长、塑封料桶中气体过多等。

芯片粘接缺陷。这些缺陷包括芯片与其基片粘接不良、粘接材料中有空洞,芯片表面有沾污(图4),造成热分布不均(局部热点)、芯片剥离或裂纹,此外,空洞还可截留潮气和沾污物。这些缺陷可导致致命失效。

钝化层缺陷。钝化层缺陷包括开裂、孔隙和粘接不良。这些缺陷会造成电气开路、中断或漏电流大。在设计芯片焊盘钝化层时,一方面要考虑到不影响键合的质量,另一方面也要注意提高集成电路焊盘抗水气腐蚀的能力。

封装缺陷。常见的封装缺陷包括气泡、粘接不良(剥离)、芯片的基片位移和引线弯曲不当。此外,模制化合物含有杂质或沾污物。这些缺陷可造成塑封开裂、金属化层变形、焊头翘起、互连线腐蚀断开、电气开路、短路或中断等等,因而使器件失效;粘接不良(剥离)是由于引线框架表面受到沾污或在键合温度下受到氧化而造成的。其他原因还包括应力消除不足和脱模剂过量等。

5 结语

提高塑封器件的可靠性是一项系统工程,其取决于固有设计、制造过程、工作条件。在设计时应当充分考虑使用环境的特性。在封装过程中,除了应加大工艺控制,如减少封装体内水汽含量,减小金属框架对封装的影响外,对塑封料的选择也是非常关键的。同时在塑封器件运输、装卸、存贮等过程中,必须采取一定的保护措施,如必要的防潮保护(防潮气侵入)、物理损伤保护(以免引线弯曲或断裂)、防静电放电保护等。