您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2025-03-11 08:34

1. 阻抗突变与信号反射

问题:高速信号线依赖精确的阻抗控制(如50Ω或100Ω差分)。邻近铺铜会改变信号线与参考平面(如地平面)的耦合关系,导致特性阻抗偏离设计值。

后果:阻抗不连续会引发信号反射,造成过冲、振铃等问题,严重时导致逻辑错误。

2. 寄生电容影响高频性能

问题:铺铜与高速线之间会形成寄生电容(尤其是平行铺铜时),电容值与间距成反比。

后果:高频信号边沿(上升/下降时间)被减缓,可能导致时序错乱。信号带宽受限,影响高速数据传输(如PCIe、DDR等)。

本质在于:原本是“带状线”,或者“微带线”,但是你把旁边铺上铜了之后,他就变了,变成了“共面波导”。

三种传输线结构:带状线、微带线和共面波导。带状线是嵌入在两个参考平面之间的信号线,而微带线则是在介质基板表面,只有一个参考平面。共面波导则是信号线两侧和下方都有接地铜皮的结构,通常设计用于特定阻抗匹配。

共面波导(Coplanar Waveguide, CPW)阻抗计算

有部分PCB板厚较厚,层数较少,利用上述方法没有办法计算出阻抗线的具体参数,这个时候就要考虑共面波导模型,这种模型是信号线参考其旁边的地线做阻抗,一般在双面板的场合用的比较多。

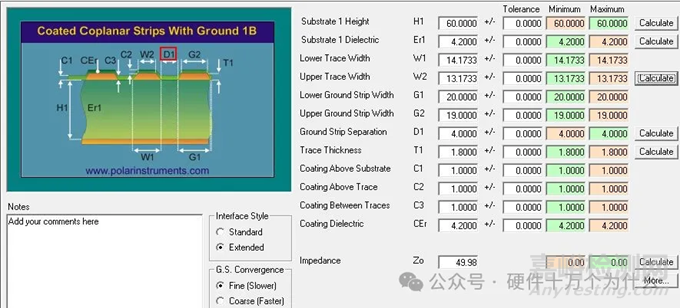

(1)单端50欧姆,选用Coated Coplanar Strips With Ground 1B模型,其阻抗计算方法如图所示,计算结构为阻抗线宽14mil,阻抗线到地线的距离4mil,地线的宽度为20mil。

50欧姆共面波导阻抗模型计算

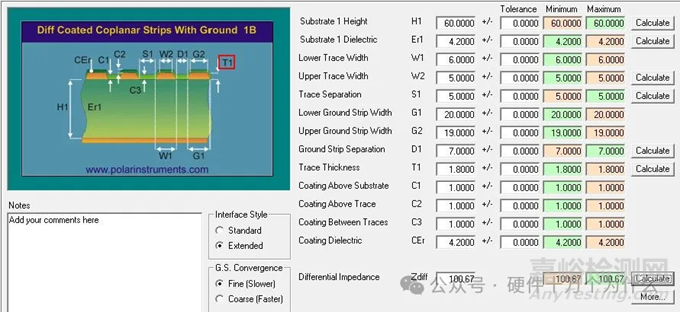

(2)差分100欧姆,选用 Diff Coated Coplanar Strips With Ground 1B,其阻抗计算方法如图所示,计算结果为100欧姆差分线宽线距为6/5mil,差分线到地线的距离为7mil,地线线宽为20mil。

100欧姆差分共面波导阻抗模型计算

(3)共面波导阻抗计算参数说明:

1.H1是阻抗线到最近参考层的介质厚度;

2.G1和G2是伴随地的宽度,一般是越大越好;

3.D1是到伴随地之间的间距。

共面波导(Coplanar Waveguide, CPW)

结构:信号线与两侧及下方的接地铜皮共面,形成“信号-地-地”的横向耦合。

电场分布:电场主要集中在信号线与两侧地铜皮之间,纵向耦合较弱。

阻抗特性:由信号线宽度(W)、与地铜皮间距(G)、介质厚度(H)共同决定,公式更复杂(需数值求解或查表)。

当在带状线或微带线旁铺铜时,无意中引入了额外的共面地结构,导致实际传输线类型变为混合模式(如“CPW+微带”或“CPW+带状线”),其阻抗特性与原始设计严重偏离。

阻抗失配:

例如,原设计为50Ω微带线(W=0.2mm, H=0.2mm, εᵣ=4.3),若两侧铺铜(G=0.1mm),可能变为CPW结构,实际阻抗可能骤降至30Ω以下。

电磁场畸变:

原微带线的场分布以垂直方向为主,变为CPW后场分布转为水平方向,加剧与邻近线路的串扰。

回流路径混乱:

在CPW结构中,回流电流可能通过两侧铜皮而非下方地平面,导致高频信号环路电感增大。

在高速PCB设计中,“铺铜导致传输线类型突变”的本质是电磁场分布和阻抗控制机制的改变。设计师需:

警惕无意识的共面波导化,通过规则约束和仿真规避风险;

在特定场景下,可主动采用CPW结构优化性能,但需精准建模。例如线宽不得不变宽(例如焊盘),则两边铺铜,来优化阻抗连续。

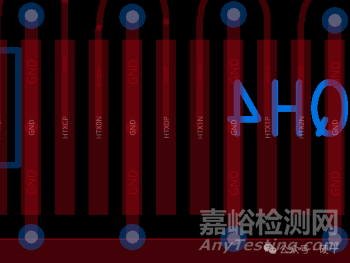

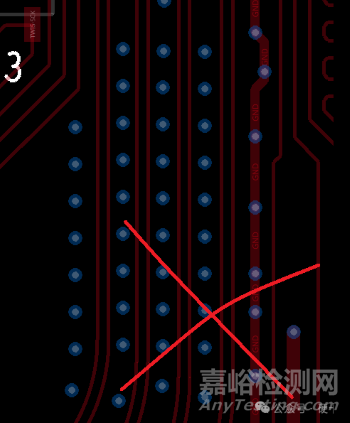

有的设计为了做高速线之间隔离,加了地线及地孔,反而把微带线变成了“共面波导”,并且间距没有控制好,造成阻抗不连续,适得其反。

来源:硬十