您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2022-04-22 01:54

从互连技术角度,SiP可分为两大类:①通过传统的芯片组装技术实现多芯片或器件的封装,如引线键合、载带自动焊(TAB) 、倒装焊等;②通过直接互连实现芯片堆叠,如通过硅通孔(TSV) 技术实现将一个芯片直接连接到另一个芯片上。

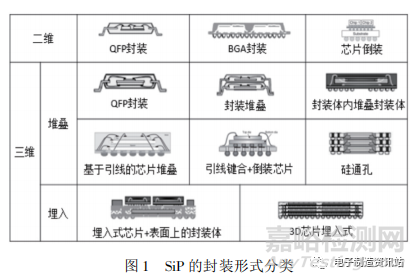

图1为国际半导体技术蓝图(ITRS) 总结的当前 SiP的主要封装结构。可以看出,系统级封装已经不再是一种单一的封装技术,这种技术包括引线键合、倒装焊、TAB、封装堆叠(PoP) 、封装嵌入(PiP) 、芯片堆叠(CoC) 、圆片级封装(WLP) 、硅通孔(TSV) 、埋入式基板等封装工艺的混合开发和集成。SiP综合了多种封装工艺,内部结构复杂,使用材料多样,这导致了其面临着更加复杂的可靠性问题。

经过多年努力,人们已对SiP的可靠性开展了大量的研究工作,并已取得了一定的成果。笔者将介绍SiP产品在热应力、机械应力和电磁干扰下的可靠性研究现状和主要失效机理,并针对航天领域使用的SiP产品,分析可靠性方面依然存在的问题,并提出相关建议。

1、SiP 的可靠性研究现状

相比单片集成电路,SiP内部复杂的封装结构以及多种芯片、元件的组合构造导致其对热应力、机械应力以及电磁干扰更加敏感,易出现失效。

1.1热应力

当芯片、元件高度集成时,产品在组装焊接时会造成温度分布不均匀;在工作时,随着内部芯片、组件产热的增加,温度会不断增加,尤其是功率型器件的存在。温度的不均匀分布以及异常高温的出现,都会对SiP内部封装结构造成损伤,不同材料之间因热膨胀系数不一致将产生热失配,界面会出现分层、裂纹等失效现象。

SiP在设计过程中主要通过热仿真的方法分析其热应力的分布情况,可能存在的热点等,据此通过更改SiP设计改善其热设计。中电29所的季兴桥利用有限元分析方法对SiP中芯片堆叠和倒装焊接两种高密度芯片组装做了热仿真分析,发现在同等环境下倒装焊芯片的温度要高于芯片堆叠封装。

台湾成功大学的Deng等利用计算流体动力学软件建立了回流焊炉子的热分布模型,通过数值模拟的方法建立SiP的共轭传热模型,进一步研究了SiP在回流焊过程中的热行为,并通过实验验证了模拟的有效性。

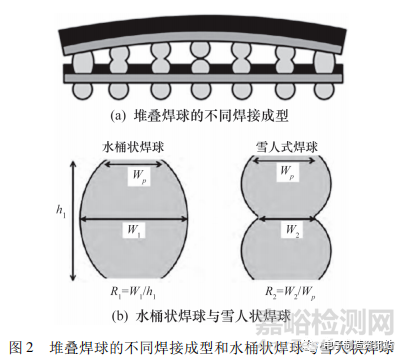

张旻澍等研究了在经历回流焊工艺后堆叠焊球的形状,发现在回流焊过程由于上层器件的翘曲,堆叠焊球会呈现出不一致的焊接成型,如图2所示,并通过模拟发现雪人式焊球的应力集中现象比水桶状焊球更加严重,同时认为现有标准无法对堆叠焊球的可靠性进行合适的测试评估。

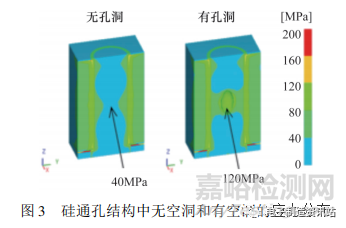

针对内部缺陷对热应力的影响,日本Toyama Prefectural 大学的 Takahiro Kinoshita 等开展了相应的研究。他们通过有限元方法分析了硅通孔(TSV) 结构中存在空洞时热应力大小及分布情况,发现热应力主要集中在空洞周围,如图3所示。

在高温状态,如果有高湿度条件的引入,塑封的SiP产品更容易出现腐蚀、爆米花、热湿应力失效。华南理工大学廖小雨研究了SiP在湿热环境下应力的分布,发现湿应力主要集中在芯片与其他材料相接触的界面处,其原因是芯片不吸湿,塑封料的湿膨胀较大以及粘结层处于基板和芯片、芯片与芯片之间。相同的湿热环境下,双芯片SiP封装可靠性受顶层芯片的影响更显著。

该课题组还通过有限元软件 Abaqus 对双芯片 SiP封装整体在温度循环条件下进行了应力应变分析,发现底层芯片、粘结层与塑封体相互接触的4个边角承受最大的应力应变。在热载荷作用下,芯片越薄,SiP封装体所承受的热应力越大; 黏结层越薄,SiP封装体所承受的热应力越小。当芯片厚度小于200μm时,热应力会明显增加,同时,SiP封装体的热应力受塑封体材料属性影响明显。

1. 2 机械应力

随着SiP在各行各业中的应用越来越广,芯片或器件的堆叠带来的机械方面的可靠性挑战也逐渐成为人们非常关心的一个问题。SiP在机械应力方面的可靠性主要涉及堆叠封装的厚度和尺寸、热失配、焊点可靠性和包封体的硬度等。

当SiP产品中堆叠的薄芯片通过引线键合实现互连时,由于键合过程会对芯片引入很大的应力,内部互连时需要对键合丝的跨度尺寸特别关注。当堆叠芯片厚度在75μm左右,很少进行引线键合,以避免芯片碎裂; 当堆叠芯片厚度增加到150μm或更大时,键合丝的跨度可达 2mm。目前,通过TSV、微凸点技术等先进堆叠工艺的应用,国内堆叠封装实现的堆叠芯片数量已经达到128层。

由于硅基芯片存在压阻效应,SiP封装引入的机械应力会影响产品的性能。由于硅晶圆、衬底、模塑化合物和粘接材料之间存在热失配,SiP在使用过程存在热-机械应力。因此选择合适的封装材料以及采用合理的工艺流程,有利于减少热-机械应力。仿真技术的引入,可对新设计的SiP产品的热失配应力进行模拟,有利于减少产品的热-机械应力。

SiP产品有复杂的互连系统,焊点的可靠性关系到异质材料间电气与机械连接的可靠性,在很大程度上决定了产品的质量。SiP在循环弯曲、跌落等机械应力作用下,主要的失效点集中在焊点位置,特别是当包封体的硬度较大时。高硬度的包封体会将更多的力传递到焊球上,加速互连失效。

除此之外,传递到内部的力会引起基板变形、翘曲,导致芯片的破碎、基板粘接分层、封装和基板间的焊接脱落等失效现象。

新加坡的Lee等在有限元仿真分析的基础上,考虑蠕变、弹性、塑性应变等多种失效机理,应用Cofin-Manson 疲劳寿命定律,成功预测各种封装焊点的疲劳强度; Kimiko Mishiro 等预测了 BGA /CSP 跌落试验的可靠性,并与仿真结果进行比较,对焊球跌落过程中受到的形变做详细的分析。

西安电子科技大学的韩培宇通过对SiP进行机械结构振动分析及可靠性计算实现了SiP系统上的芯片位置和尺寸的优化。

1. 3电磁干扰

SiP作为高度集成的封装技术,存在高速、高密度、高功耗、低电压和大电流的发展趋势,产品的抗电磁干扰能力对新产品的成败起到关键性的作用,其中电源分布网络(PDN) 设计和电源完整性(PI) 研究的挑战日益严峻。

理想的电源供给系统提供的电压是一个恒定值,但是,实际的供电系统并不是稳定的。这是因为供电网络是一个分布式网络,存在大量的寄生电阻、寄生电感、寄生电容以及导纳等。

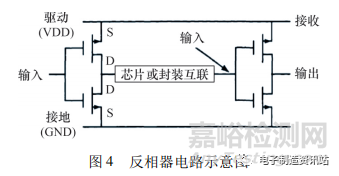

图4显示了一个串联反相器示意图。其中,晶体管的栅极为输入端,漏极为输出端。而晶体管的栅极可以等效成一个MOS电容( 金属-氧化物-半导体衬底) 。

在电路开关时,电容包括两个过程:达到“1”电平的充电过程和达到“0”电平的放电过程。电路运行速度的快慢是由开关时电容充放电的速度决定的,而电源和地引线上的寄生电阻和寄生电感会降低电容的充放电速度。

因此设计低阻抗的供电系统能有效保障为芯片提供稳定的电压和电流。而数字电路的开关电路或模拟电路工作中的瞬态电流经由PDN产生瞬态开关噪声(SSN) 引起的电压波动会严重影响晶体管的工作状态:

① 当芯片电源引脚间的电压过小时,会阻止晶体管的翻转;

② 当芯片电源引脚间的电压过大时,也会产生芯片工作可靠性问题;

③ 电压波动耦合到静止的晶体管电路,可能会引起信号的误触发;

④ 电压波动会引起的驱动器输出波形延时,严重时也会产生信号的时序问题,表现为数字电路中的抖动。

随着芯片堆叠数量的增加,I /O互连密度的增加,SiP产品在设计过程中需要着重研究电源完整性、信号完整性和电磁干扰(EMI) 。

其中,电源完整性涉及电源分布网络设计中功率噪声的降低、电压波动的抑制等;信号完整性(SI) 主要是经由 PND传导引起的系统噪声问题;电磁干扰主要来源于电源/地平面间谐振引起的边缘辐射和三维混合芯片堆叠芯片间电感性耦合。

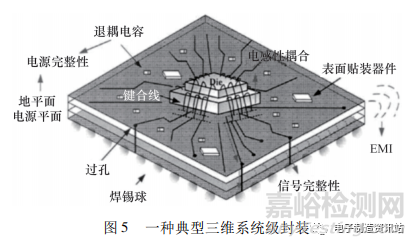

图5为一种典型的三维系统级封装示意图,清楚地描绘了系统级封装中存在的电源完整性、信号完整性和电磁干扰问题。通过SiP中叠层顺序的变化、缩短敏感芯片的键合丝长度、减少键合丝等技术改进不仅能改善信号完整性,而且能削弱电磁干扰。

针对电磁干扰对SiP可靠性的影响,目前大多数是从产品本身结构设计、工艺改进等技术手段提升其电磁兼容能力,外部电磁环境干扰对SiP可靠性影响的文献研究相对较少。

2、SiP 的失效机理

失效机理是指引起电子产品失效的物理、化学过程。导致电子产品失效的机理主要包括疲劳、腐蚀、电迁移、老化和过应力等物理化学作用。失效机理对应的失效模式通常是不一致的,不同的产品在相同的失效机理作用下会表现为不一样的失效模式。

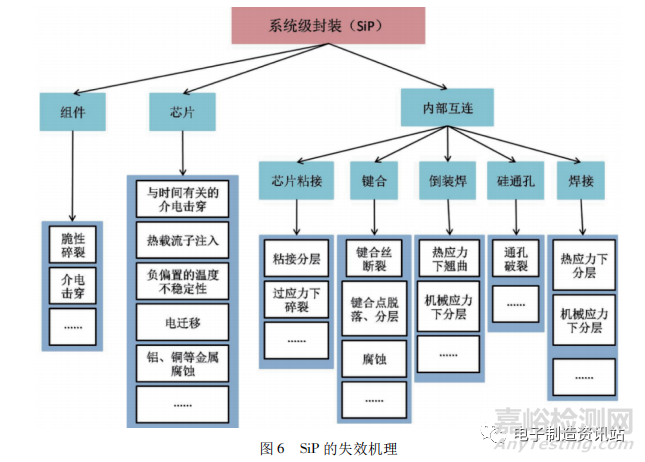

SiP 产品引入了各类新材料和新工艺,特别是越来越复杂与多样化的界面和互连方式,这也必然引入新的失效机理与失效模式。SiP的基本组成包括芯片、组件和互连结构。不同功能的芯片通过粘接等方式安装在基板上,电学连接是通过键合丝键合、倒装焊、粘接、硅通孔等方式实现的。

根据SiP的内部结构组成,图6展示了其主要的失效机理。

随着电子产品向高密度集成、功能多样化、小尺寸等方向发展,传统的失效分析方法已不能完全适应当前技术发展的需要。为了满足SiP产品的失效分析,实现内部互连结构和芯片内部结构中失效点的定位,分析技术必须向高空间分辨率、高电热测试灵敏度以及高频率的方向发展。

目前,半导体器件失效分析的试验项目及相关设备主要有以下几种。

① 外部目检: 光学显微镜、扫描电子显微镜和电子探针。

② 电特性测试: 器件功能测试机台和半导体参数分析仪。

③ 无损分析: X-ray、扫描声学显微镜(C-SAM) 、密封性检查以及粒子碰撞噪声测试仪(PIND) 。

④ 内部目检及失效定位: 酸腐蚀开盖机、机械探针测试台等。

为了更好地满足SiP产品的失效定位,3DX-ray、同步热发射(LIT) 和磁显微术等非破坏性缺陷检测及定位技术以及液晶热点检测、红外成像、微光显微术(EMMI) 、激光束电阻异常侦测技术(OBIRCH) 、聚焦离子束等破坏性缺陷检测及定位技术不断被开发应用。

来源:旺材芯片