您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2022-10-13 14:29

集体电路(IC) 发明至今已有50多年,自1991年问世以来,国际半导体技术蓝图(International Technology Roadmap for Semiconductors,ITRS) 一直是半导产业往前迈进的指南,蓝图预测半导体技术会遵循摩尔定律(Moore's Law) 的缩放节奏迈进。不过,在2016年7月ITRS所释出的半导体产业「未来蓝图」报告显示,估计微处理器中的晶体管体积将在2021 年开始停止缩小,这意味着微处理器中的晶体管数量将不会再如摩尔定律所说的会逐步增加,也就是说摩尔定律已宣告死亡。随着摩尔定律的死亡,国际半导体技术蓝图ITRS也将步入历史。取而代之的,将是异构整合蓝图(Heterogeneous Integration Roadmap,HIR)。

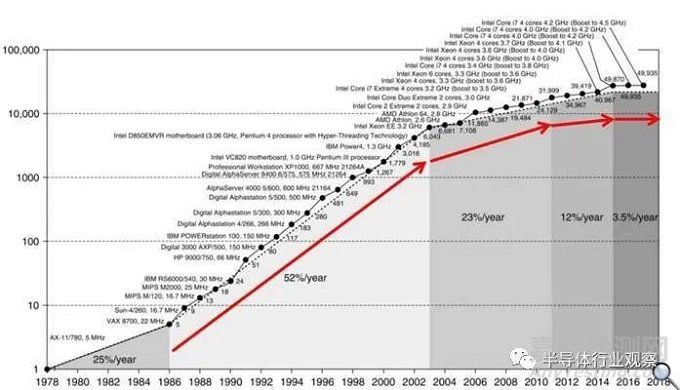

虽然芯片设计和制程技术的创新仍然继续,但进展已明显趋缓,不管制程技术下杀到多少微米,芯片尺寸的缩减似乎已到了极限,更遑论同时要增加密度以提升性能。图1及图2是Alphabet的总裁John Hennessy 于2018 年7 月ERI会议中展示的两张图表。图1显示了40年间的DRAM的容量和密度增长放缓的情况;而图2则显示了40年间的CPU运算性能变化,明显看出在近年成长已趋于平稳。

图1. 40年间的DRAM的容量和密度增长放缓的情况(资料来源:J Hennessy, ERI Conf July 2018)

半导体产业协会(SIA) 于2016年7月正式宣告ITRS国际半导体技术蓝图时代的结束。其后SIA 和SRC (半导体研究公司,Semiconductor Research Corporation)于2017 年3 月联合发表了名为《半导体研究机会:产业愿景和指南》报告(Semiconductor Research Opportunities:An Industry Vision and Guide)。报告中指出:「前进的道路并不像摩尔定律时代那样清晰,然而,巨大的经济和社会效益潜力— 其中一些是可以预见的,但有一些只能想像…… 在这个关键点上,需要产业界、政府和学术界携手合作,才能持续进步成长。」

图2. 40年间的CPU运算性能成长,近年已趋缓

(资料来源:J Hennessy, ERI Conf July 2018)

应用及市场需求带动

在今天,电子产品已深深融入我们的社会结构,改变着我们的生活、工作和娱乐方式,让我们生活在数位时代,为我们的全球生活方式、产业和商业行为带来高新的效率。而这种效率的达成主要归功于高效能运算芯片的产出。另一方面,大数据的形成则推动了市场需求,从而形成了技术研发的驱动力。

在现实层面,推动数据增长的市场力量包括:

将数据、逻辑和应用程序转移到云端

社交媒体的推波助澜

行动设备的演变

5G/6G 通信加上物联网(IoT)带动

人工智能(AI)、虚拟现实(VR)及增强现实(AR)的应用

自动驾驶汽车的兴起及日渐普及

异构整合兴起

虽然制程技术的演进已渐渐无法满足芯片「体积缩小性能提升」的无止境需求,但需求并没有消失,因此,人们开始往构装技术动脑筋。

异构整合是指将单独制造的「组件」整合到更高层次的组装(系统级封装- System in a Package,SiP),以使整体性能提升。系统级封装不是随便将两个芯片封装在一起就可以,而是必须满足下列条件才行:

封装后体积必须变小:将不同功能的芯片与被动元件封装成一颗IC,所以封装后体积必定比个别数颗IC还小。

须整合不同类型的封装技术:必须将数种不同类型的封装技术整合在一起,与单纯将多个芯片封装在一起的小型封装技术不同。

必须包含各种类型的主动与被动元件:必须包含处理器、记忆体、逻辑元件、类比元件等数个芯片,甚至必须将被动元件、连接器、天线等一起封装进去。

在异构整合的定义中,「组件」指的是任何单元,无论是单颗芯片、MEMS器件、被动元件和组装的封装或子系统,都整合在一个封装中。当中可以涉及到材料、元件类型、电路类型、节点、互连方法……等等。

图3. 异构整合(图左) 及系统级封装(图右)

(资料来源:日月光半导体)

大厂纷纷投入

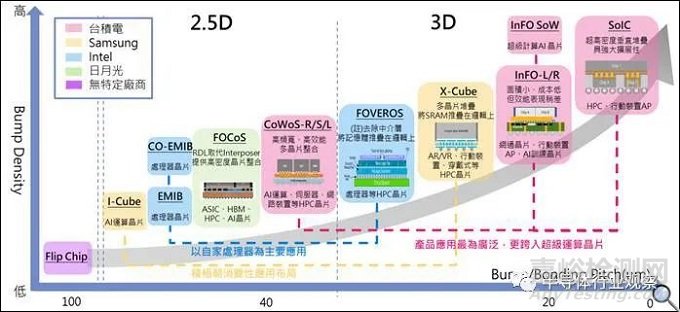

在芯片堆叠密度增长及多芯片整合的需求下,大厂纷纷投入先进封装技术的发展。其中又以运算芯片制程大厂Intel、TSMC及Samsung的投入最为理所当然。这些大厂将其先进制程技术所产出的芯片配合自家的先进封装,来完成客户的产品;而封测大厂日月光则是从本身的封装技术出发,慢慢发展出2.5D及3D之先进封装技术(图2)。

从图2可见,整体来看,TSMC目前是站在比较领先的地位,从2.5D到3D封装都有相当完整的技术。另一方面,Intel的Foveros及EMIB也逐渐形成了一个平台。

由于先进封装要求的技术很高,因此很多大厂也相应的在这方面投入很高的资本支出。从图3可见,2022年的资本支出已达到10 ~ 40亿的等级。目前各大厂都有本身的技术平台,而最近产出的新产品也不少。

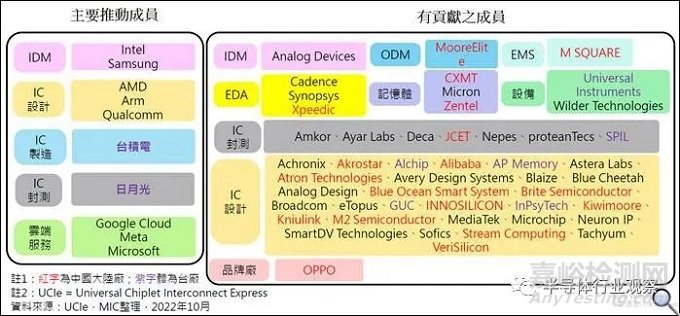

而其中一个于2022年最重要的动态是Intel于2022年3月邀请了台积电、Samsung、AMD、Microsoft、Google、日月光等大厂共同组成及推动UCIe小芯片联盟,有助于小芯片(Chiplet)资料传输架构的标准化;未来在UCIe小芯片联盟的推动下,会越来越趋向标准化,从而降低小芯片先进封装设计的成本。

此外,透过制定统一的小芯片/晶粒(Die)间传输规范,以落实晶粒「随插即用(Plug and Play)」的目的,使来自不同厂商、代工厂的晶粒能在单一封装内顺利整合,一定程度上满足了高阶运算芯片持续提升运算单元密度以及整合多元功能的需求,成为开发高阶运算芯片的关键。

UCIe自成立以来,已有数十家包含IC设计、封测、材料设备、电子设计自动化系统等不同类型的业者纷纷加入,显示小芯片先进封装的跨领域特性。从图4可见,图右的贡献会员除了IDM、IC封测及IC设计厂商外,还有EDA、ODM、记忆体、EMS及终端产品厂商, 显示UCIe联盟的影响力越来越广。。

小芯片联盟先导的推动成员在标准主导上占了一定的优势,像Intel便推出了自己的开放式小芯片平台,如图6左边部分所示,可以用Intel自家的CPU去整合客户的小芯片,辅以Intel本身的2.5D、3D技术去完成完整的封装;而这就是Intel推动其IDM 2.0一个很重要的助力,提供了一个平台可让Intel进行代工及封测服务。

不过,联盟成员也不会独厚Intel,目前已提供了成员数个小芯片封装可用的架构,包括图6右边的标准2D封装架构及2.5D封装架构 (可参考Intel的EMIB、TSMC的CoWoS及日月光的FOCoS)。

大厂技术

经过长时间的研发,先导大厂的异构整合先进封整产品均已开始提供服务,像TSMC台积电从CoWoS、InFO,到SoIC,已经累积丰富的先进封装经验,形成3D Fabric平台;台积电透过3D Fabric平台,整合2.5/3D先进封装技术,为顶级客户客制最佳化产品,透过绑定先进制程,提供先进制程代工到先进封装的一条龙服务,主要产品类别为HPC高效能运算与高阶智慧型手机芯片。

就Intel的部分,前面已经提过,发展先进封装技术为Intel IDM 2.0策略中关键的一环。近期Intel陆续推出2.5D封装的嵌入式多芯片互连桥接(Embedded Multi-die Interconnect Bridge, EMIB)技术、3D堆叠的Foveros技术,以及整合2.5D与3D封装的共嵌入式多芯片互连桥接Co-EMIB技术。Intel的Foveros 封装技术利用3D 堆叠整合不同的逻辑芯片,为IC设计公司提供了很大的灵活性,允许其将不同技术的IP 区块与各种记忆体和I/O 元件混合和搭配。Intel的Foveros可以让芯片产品分解成更小的小芯片(chiplets) 或细芯片(tiles),其中I/O、SRAM 和电源传输电路整合在基础芯片中,而高性能逻辑小芯片则是堆叠在顶部。

至于记忆体大厂Samsung则是提供记忆体堆叠异构整合封装服务,包括其在2020 International Wafer-Level Packaging Conference (IWLPC)中展示的记忆体堆叠(Memory Stack)异构整合技术,以及其「X-Cube (eXtended-Cube)」3D封装技术,包含把记忆体与其他芯片整合,以及硅穿孔、微凸块等关键技术。

来源:半导体行业观察