您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2024-09-25 08:11

在芯片的失效分析中,有很多时候在板是故障的,但是拆下来后测试单体却又是正常的,导致这种现象主要有两种可能:

1)芯片的故障不稳定,典型案例如键合缺陷

2)板上时序存在问题,导致芯片功能异常

本文将对针对第2种情况,找一个典型案例进行剖析分享。

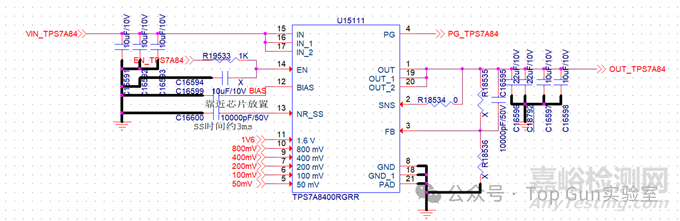

问题背景:某板卡LDO故障,设计输出0.8V,实际输出1.3V,故障率20%

核对原理图设计未见明显异常,将芯片拆下后进行分析,IV测试和bench测试均未见明显异常,bench测试与良品表现一样

单体分析结论:芯片“大概率”是良品,因此返回到板级分析。

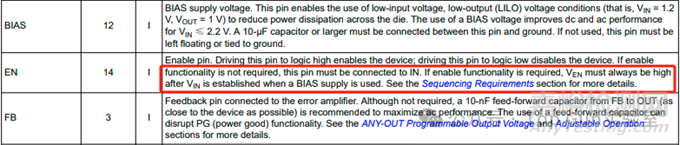

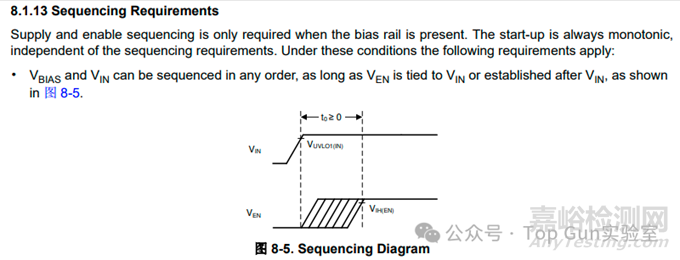

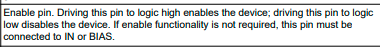

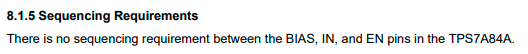

断开LDO后级负载,故障现象未消失;查看器件规格书对EN和Vin上电时序有要求,该板设计EN管脚不是直连Vin,怀疑可能LDO的上电时序存在问题。

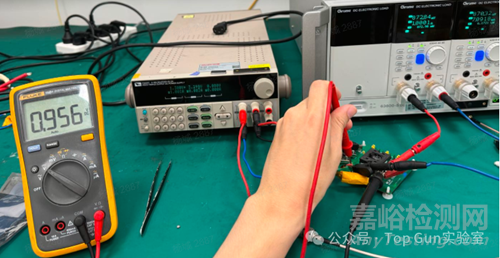

时序确认:对板卡LDO上电时序进行测试,确认时序存在问题。

改善:通过飞线方式,将EN直连Vin,“故障”芯片恢复正常,确认为板卡设计问题导致芯片异常。

拓展:

1)在进行板级设计时,需要考虑芯片上电时序,此类问题在我的印象中是仅次于EOS的类型,且此类问题分析需要跨专业域协同,耗时耗力。

2)查看TI官网,发现3A的的LDO有两个版本,另一个就对芯片上电时序没有要求。

TPS7A84A上电时序要求:

总结:失效分析作为一门专业性极强的学科,拥有着典型且具有显著规范性的失效分析流程与方法。但是,在实际的操作过程之中,绝对不能不加思索、盲目地去生搬硬套既定的分析流程,而是应当紧密地结合具体的实际状况,展开全面且深入的分析以及富有逻辑性的思考。就拿同样都是故障不复现的问题来说,在到底应当如何去制定下一步的分析思路这一关键方面,不同的案例彼此之间是存在着巨大且完全不同的差异的。

来源:Top Gun实验室