您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2025-01-24 17:07

目前在电子行业中,计算机芯片表面可容纳的晶体管数量已趋近极限。芯片制造商开始寻求新的晶体管数量增长途径。业界希望把晶体管和半导体元件堆叠于多个表面,如同将平房改建成高楼一般。这种多层芯片能够处理海量数据,执行比现有电子产品更为复杂的功能。然而,芯片构建平台成为一大阻碍。任何可堆叠芯片都需包含厚厚的硅 “地板” 作为各层的一部分,这会使功能性半导体层之间的通信速度减缓。

美国

近日,美国麻省理工学院的工程师们成功攻克这一难题,他们开发了无缝堆叠电子层的方法,可以制造出速度更快、密度更高、性能更强大的计算机芯片。研究人员将两种不同的过渡金属二硫化物(TMD)层二硫化钼和二硒化钨直接交替堆叠,可成倍增加芯片上的晶体管数量,不需要任何硅晶片基板,从而实现更好、更快的层间通信和计算,且工作温度低。此方法让工程师可以在任意随机晶体表面构建高性能晶体管、内存和逻辑元件,而非局限于硅晶片的厚重晶体支架。研究人员指出,没有厚硅基板,多个半导体层能够更紧密接触,实现更优、更快的层间通信与计算。

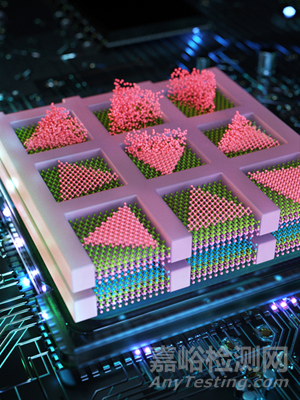

图:该团队将半导体粒子(粉色部分)以三角形的形式沉积在密闭的正方形内,以创建高质量的电子元件,直接位于其他半导体层(紫色、蓝色和绿色层)之上。

研究人员预计,该方法可应用于构建人工智能硬件,例如以笔记本电脑或可穿戴设备的堆叠芯片形式呈现,其速度与功能将与当今超级计算机相当,数据存储量可媲美物理数据中心。“这一突破为半导体行业带来巨大潜力,使芯片堆叠摆脱传统限制,” 研究作者、麻省理工学院机械工程副教授 Jeehwan Kim 表示,“这可能大幅提升人工智能、逻辑和内存应用的计算能力。”

2023年,研究团队为在非晶涂层硅晶片生长 TMD,促使原子排列成高质量单晶形式而非随机多晶无序形式,在硅晶片上覆盖一层极薄的二氧化硅“掩模”。但该方法仅在 900℃ 左右有效,容易伤害底层电路。因此在新研究中,研究人员为在低温下生长单晶二维材料以保护底层电路,从冶金学找到办法。冶金中熔融金属倒入模具,液体会在边缘优先 “成核”,形成规则晶体。研究人员将此概念用于 AI 硬件,继续用二氧化硅掩模覆盖电路,在掩模 “口袋” 边缘沉积 TMD “种子”,发现边缘种子在低至 380℃ 就能长成单晶材料,而中心种子则需更高温度。研究人员进一步利用该方法制造出多层芯片。

研究人员称,该方法可使芯片半导体元件密度翻倍,对现代逻辑电路基本构成的金属氧化物半导体(CMOS)尤是如此,并称,用此技术能造出 3D 逻辑芯片、3D 内存及其组合,可生长堆叠数十到数百个逻辑层与内存层。且传统 3D 芯片依靠硅晶圆钻孔制成,限制了堆叠层数量、垂直对准分辨率和成品率,而新的材料生长方法能一次性解决这些问题。为进一步推动可堆叠芯片设计商业化,研究团队创立了一家 “FS2”(未来半导体 2D 材料)公司,下一步将扩大规模,从展示小型设备阵列过渡到专业 AI 芯片操作。

研究得到了三星先进技术研究所和美国空军科学研究办公室的支持。相关研究成果发表在《自然》期刊。

来源:综合消息