您当前的位置:检测资讯 > 生产品管

嘉峪检测网 2018-06-14 09:41

设计是电子工程师在设计中遇到常见难题,电磁兼容性(EMC)是指设备或系统在其电磁环境中符合要求运行并不对其环境中的任何设备产生无法忍受的电磁干扰的能力。因此,EMC包括两个方面的要求:一方面是指设备在正常运行过程中对所在环境产生的电磁干扰不能超过一定的限值;另一方面是指器具对所在环境中存在的电磁干扰具有一定程度的抗扰度,即电磁敏感性。 所谓电磁干扰是指任何能使设备或系统性能降级的电磁现象。而所谓电磁干扰是指因电磁干扰而引起的设备或系统的性能下降。

EMC包括EMI(电磁干扰)及EMS(电磁耐受性)两部份,所谓EMI电磁干扰,乃为机器本身在执行应有功能的过程中所产生不利于其它系统的电磁噪声;而EMS乃指机器在执行应有功能的过程中不受周围电磁环境影响的能力。

在电子产品的设计中,为获得良好的EMC性能和成本比,对产品进行EMC设计是重要的;电子产品的EMC性能是设计赋予的。测试仅仅是将电子产品固有的EMC性能用某种定量的方法表征出来。对于EMC设计来讲:

首先,应在研发前期考虑EMC设计。

如果产品设计前期不考虑EMC问题,仅寄希望于测试阶段解决(表现为通过整改来解决设计成型产品的EMC问题,这样大量的人力和物力都投入在后期的测试/验证、整改阶段)。那么,即使产品整改成功,大多情况下还是会由于整改涉及电路原理、PCB设计、结构模具的变更,导致研发费用大大增加,周期大大延长。只有在前期产品设计过程中考虑与预测EMC问题,把EMC变成一种可控的设计技术,并行和同步于产品功能设计的过程,才能一次性地把产品设计好。

其次,应该系统化的进行EMC设计。

通过设计提高电子产品的EMC性能,绝对不是企业内EMC专家一个人所赋予的,因为EMC绝对不可能脱离产品硬件、结构等实物而存在。因此,要使设计的电子产品一次取得良好的EMC性能,就需要提高产品设计工程师的EMC经验与意识问题。如硬件工程师,除了原先必须掌握的电路设计知识外,还应该掌握EMI和EMS抗干扰设计的基本知识;PCB设计工程师需要掌握相应的器件布局、层叠设计、高速布线方面的EMC设计知识;结构工程师也需要了解产品结构的屏蔽等方面的设计知识。因为这些共同参与产品设计的工程师,要去实现FMC专家在产品设计过程中所提出的意见,就要理解、领会EMC专家所提出的建议的奥秘,并与各自领域的设计特点相结合,将所有EMC问题的萌芽消灭在产品设计阶段。只有所有参与产品设计的开发人员共同提高EMC素质,才能设计出具有高性能EMC的电子产品。

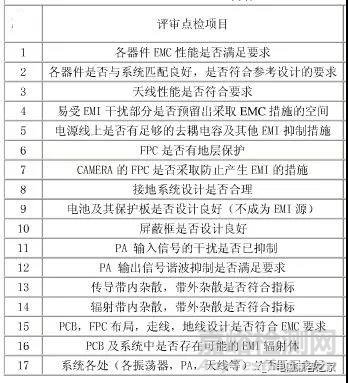

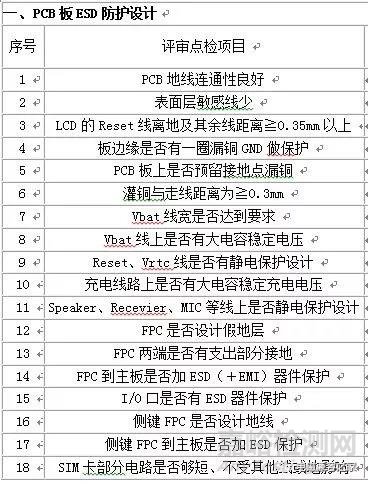

一般电子产品设计时不考虑EMC问题,就会导致EMC测试失败,以致不能通过相关法规的认证。下图概述了EMC、EMI、ESD评审的要点。

EMC、EMI、ESD评审的要点

EMC、EMI、ESD评审的要点

随着电气电子技术的发展,家用电器产品日益普及和电子化,广播电视、邮电通讯和计算机及其网络的日益发达,电磁环境日益复杂和恶化,使我们逐渐关注设备的工作环境,日益关注电磁环境对电子设备的影响,电气电子产品的电磁干扰(EMI)和电磁兼容性(EMC)的问题越来越受到工程师和生产企业的重视。在ESD防护中,大体可以分为两大类。

传导性ESD防护

对静电电流在电路中防护主要使用一些保护器件,在敏感器件前端构成保护电路,引导或耗散电流。此类保护器件有:陶瓷电容,压敏电阻,TVS管等。

辐射性ESD防护

对于静电产生的场对敏感电路产生影响,防护方法主要是尽量减少场的产生和能量,通过结构的改善增加防护能力,对敏感线路实施保护。对场的保护通常比较困难,在改良实践中探索出了一种叫做等位体的方法。通过有效地架接,是壳体形成电位相同体,抑制放电。事实证明此种方式有效易于实施。

防护静电的一般方法有许多,包括减少静电的积累;使产品绝缘,防止静电发生;对敏感线路提供支路分流静电电流;对放电区域的电路进行屏蔽;减少环路面积以保护电路免受静电放电产生的磁场的影响。有针对直接放电的,也有针对关联场的耦合。

来源:AnyTesting