您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2024-04-25 19:22

【源起】 产品出现早期失效,或安装后上电不正常,或运行几个月就失效。从时间角度看,属于早期失效。通过分析,是芯片失效,在边沿出现了裂纹,扩展到有源区造成功能失效。为什么会遗留到市场,并且还出现不同型号的失效,不好根治。加应力筛选效果也不明显。

(裂纹示意图)

【简要分析】

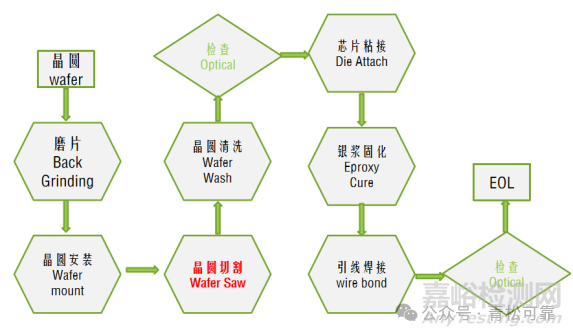

BGA封装的前段工艺简图:

晶圆加工后有磨片、晶圆安装、切割、银浆固化、引线焊接等环节都可能造成芯片裂,从工序看,到最后封装还有两道工序检测,以及到最后还有测试,怎么没有把问题检测出来呢?在案例中,主要关注“晶圆切割”(Wafer Saw)工艺带来的问题以及遗留到后端的分析。

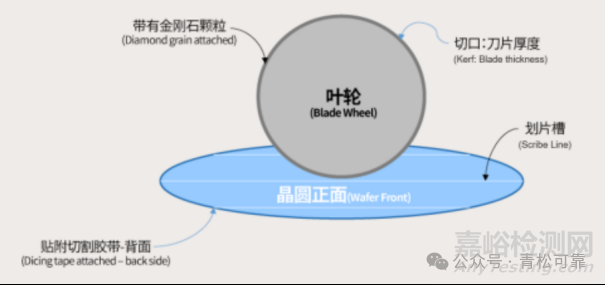

(网上示意图)

晶圆主要是Si,脆性材料,与切刀相碰,如果裂纹过长,就可能延伸进芯片有源区,造成失效。下面对案例总结简要说说。

DIE SAW 失效案例对比分析总结

当半导体工艺缩小后,介质层用 low k,承受强度降低,一些新性能的芯片厂家接连出现问题,对处理的一些案例进行总结分析:

1、失效形貌基本相似,裂纹的严重程度不同。

2、失效根因不同,但最终影响相似。

3、失效阶段:器件不一定在生产表现出来,在市场失效属于早期失效。

4、对失效批次的样品进行可靠性实验,激发应力:对于DIE SAW裂纹,带湿度的应力比纯温度变化应力更有效;在分层较严重时,温循有一定激发效果。

5、裂的原因:DIE SAW 工序后芯片边沿存在裂纹。裂纹大小与设计、工艺、设备的差异相关,如果先前芯片边沿结构设计考虑不周,工艺过程管理的一致性不好,“裂纹”长度超过一定范围,就会在后续加工应力及工作应力作用下扩展,最终造成失效。

6、健壮设计与验证:用 low K材料后边沿/转角的结构设计,工艺设计完备性要考虑,用合适 的DOE验证方案明确要监控的工艺过程参数。

DIE SAW 相关设计主要要素:

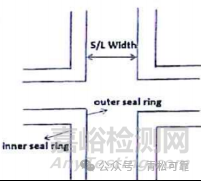

1、切割道宽度设计,基于具体工艺和技术要明确风险。

2、芯片边角设计:芯片边角要有个三角避空位置。

DIE SAW 工艺设计主要要素:

1、不同工艺节点切割刀的选取;

2、激光切口形状的确认,涂覆液的选型,激光灼伤的判定标准等;

3、对于激光切割的关键参数要开展DOE实验验证确定并明确相关要求;

4、对于双刀分步切割工艺,第二刀的要求也要细化。

5、对切口宽度要实时监控和SPC管控(CpK>1.67),保证相应裕量。

6、切割后wafer要进行表面杂质清洗工序并有明确要求。

更详细的要结合厂家的材料、工艺及设备进行分析、实验验证,最终实现裂纹要满足要求。

检测与实验:

1、边缘裂纹的检测不能通过电性能测试,也没有自动化。不知现在是否可以借助光学检测+AI 来实现,避免人眼的疲劳,同时提高效率。

2、边沿与保护环距离标准差异,如5um,还是6um,是否能够达成一致?换一个角度看,整个生产过程(包括不同批次,换刀等环节)保证工艺和结果一致性更重要。

简要写下这些,具体到原理分析和设计,涉及不同结构,比较复杂,后续持续跟进。

来源:青松可靠