您当前的位置:检测资讯 > 科研开发

嘉峪检测网 2024-12-22 20:12

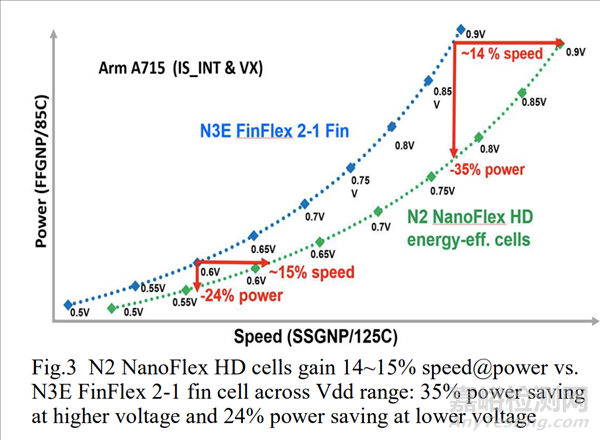

IEDM 2024大会上,台积电首次披露了N2 2nm工艺的关键技术细节和性能指标:对比3nm,晶体管密度增加15%,同等功耗下性能提升15%,同等性能下功耗降低24-35%。

曝料称,台积电N2目前的良率已经达到了60%,而不久前,一位台积电员工对外透露,已成功将N2测试芯片的良率提高了6%,为公司客户“节省了数十亿美元”。

当然,这一数据还有较大提升空间,通常芯片良率需要达到70%或更高才能进入大规模量产阶段。

作为对比,消息称三星的2nm工艺良率目前仅在10%-20%之间。

台积电研发和先进技术副总裁Geoffrey Yeap表示,N2是台积电“四年多的劳动成果”。

台积电2nm首次引入全环绕栅极(GAA)纳米片晶体管,有助于调整通道宽度,平衡性能与能效。

如今的FinFET晶体管的核心有一个垂直的硅片,而全环绕栅极纳米片晶体管有一堆狭窄的硅带。

FinFET只能通过乘以器件中的翅片数量来提供这种多样性,例如具有一个、两个或三个翅片的器件。

但全环绕栅极纳米片为设计人员提供了介于两者之间的渐变选择,例如相当于1.5个翅片或任何可能更适合特定逻辑电路的东西。

新工艺还增加了NanoFlex DTCO(设计技术联合优化),可以开发面积最小化、能效增强的更矮单元,或者性能最大化的更高单元。

此外还有第三代偶极子集成,同时包括N型、P型,从而支持六个电压阈值电平(6-Vt),范围200mV。

通过种种改进,N型、P型纳米片晶体管的I/CV速度分别提升了70%、110%。

对比传统的FinFET晶体管,新工艺的纳米片晶体管可以在0.5-0.6V的低电压下,获得显著的能效提升,可以将频率提升大约20%,待机功耗降低大约75%。

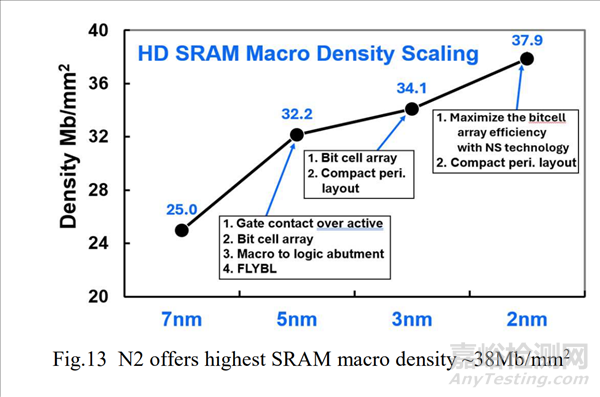

SRAM密度也达到了创纪录的新高,每平方毫米约38Mb。

根据最新曝光的资料显示,Intel 18A工艺的SRAM密度约为每平方毫米31.8Mb,显然远不如台积电2nm,落后了超过16%。

同时,2nm的这一密度也比N3 3nm工艺下提高了11%,而N3只比自己的前代提高了6%。

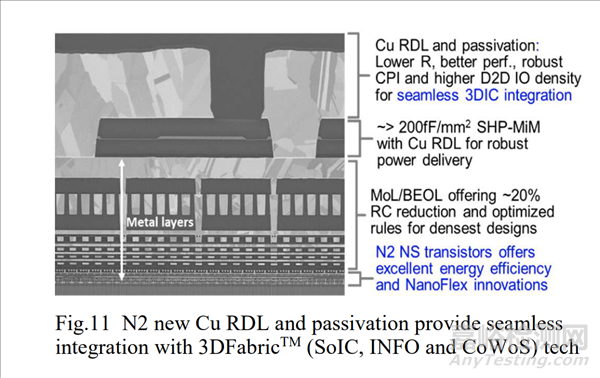

此外,台积电2nm还应用了全新的MOL中段工艺、BEOL后段工艺,电阻降低20%,能效更高。

值得一提的是,第一层金属层(M1)现在只需一步蚀刻(1P1E)、一次EVU曝光即可完成,大大降低了复杂度、光罩数量,提高了整体工艺效率。

优化的M1采用新的1P1E EUV图形,使标准电池电容降低了近10%,并节省了多个EUV掩模。

针对高性能计算应用,台积电2nm还引入了超高性能的SHP-MiM电容,容量大约每平方毫米200fF,可以获得更高的运行频率。

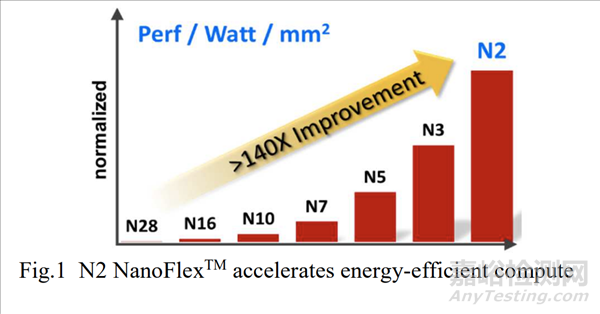

按照台积电的说法,28nm工艺以来,历经六代工艺改进,单位面积的能效比已经提升了超过140倍!

目前,台积电N2处于风险试产阶段,计划2025年下半年量产。

同时,台积电还在研发N2P,也就是N2的增强版本,预计带来5%的性能提升,并完全兼容N2,计划2025年完成资格认证阶段,2026年量产。

随着台积电N2的量产,2nm晶圆的代工报价可能将达到2.5万-3万美元/片(约合人民币14.6万-21.9万元),远高于当前3nm晶圆约2万美元/片的价格。

公开报道显示,2004年台积电发布90nm工艺的时候,彼时晶圆报价近2000美元,而制程技术到2016年演进至10nm后,报价增幅显著,达到6000美元。

进入7nm、5nm制程世代后,报价破万,5nm更是高达16000美元,且该统计价格尚未计入台积电2023年6%的涨幅。

iPhone 18 Pro系列将首发搭载A20 Pro处理器,而这颗芯片回首发台积电2nm工艺制程,芯片价格由目前的50美元上涨至85美元,涨幅高达70%、

随着成本的上涨,iPhone 18 Pro最终售价可能会涨。

在今年10月份,高通、联发科旗舰芯片全部转向3nm工艺制程,相关终端掀起了一轮涨价潮,半导体业内人士预计,由于先进制程报价居高不下,芯片厂商成本高企,势必将成本压力转嫁给下游客户或终端消费者。

来源:硬件世界